First things first – Timing Graph – Part 2

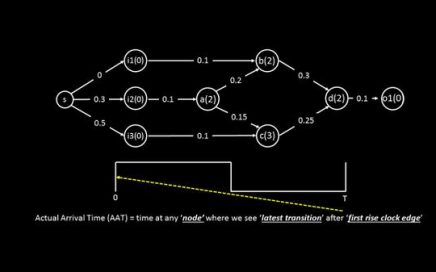

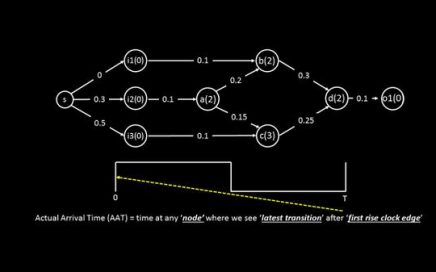

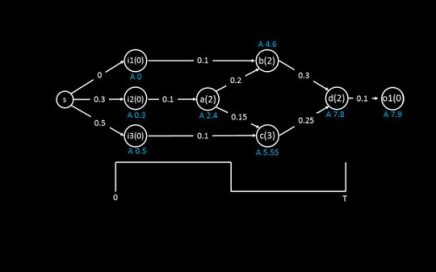

Hello Now that we know what a timing graph is, let me unveil actual arrival time (AAT), required arrival time (RAT) and slack. We have […]

Hello Now that we know what a timing graph is, let me unveil actual arrival time (AAT), required arrival time (RAT) and slack. We have […]

Hello This is like the ‘Batman’ of static timing analysis. We have heard stories about it but never seen it. The reasons, this comes more […]

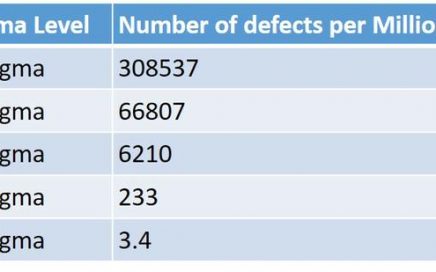

Hello Let me start with a quote “Competition is always a good thing. It forces us to do our best. A monopoly renders people complacent […]

Hello Japanese stood to be the world leaders during 1980-1990 regime in semiconductor manufacturing [2]. During my research, I found that Japanese semiconductor firms are […]

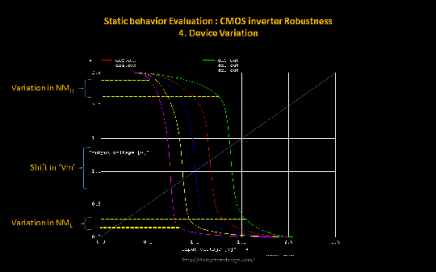

Hello – In my last post, I was very happy about the robustness of CMOS logic. And here’s more reason to be happy to discover what […]

Hello It’s so robust… I can give you 4 instances of this 1) Vary PMOS width size to its maximum, keeping NMOS width constant and […]

Hello We were looking for a solution for below scenario, and you will be amazed to see, how an ‘Universal Gate’ solves the below problem […]

Hello And here’s the solution to the problem posted in my previous article. ‘AND gate itself’. If you observe carefully, you tie one of the […]

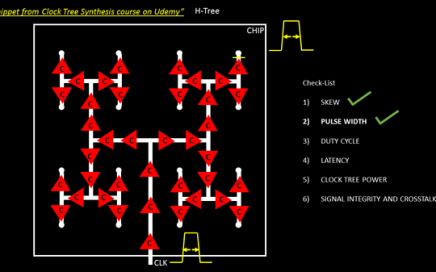

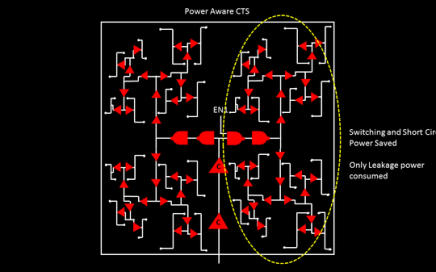

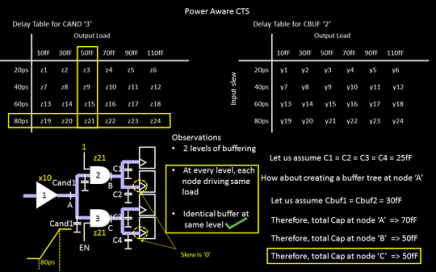

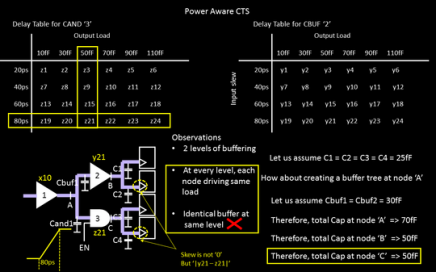

Hello While trying to build a clock tree which is power aware, let’s go back a step ahead and look, what are the top observations […]

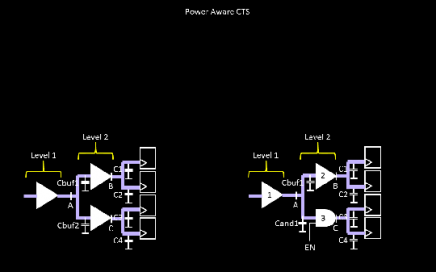

Hello How about saving some power for the below clock tree network ? It’s tricky and if we go with the right approach, we might […]