2nd mile-stone in field open-source (efabless open-lane EDA + Google/Sky130 open-process)

GitHub is indeed the new RESUME for VLSI industry. Really, if you looking forward to judge a new candidate for a role in your company, ask for GitHub project link. Projects written on resume and projects available on GitHub by a candidate will immediately give you an idea about his/her perseverance, dedication, sincerity, productivity and amount of hard-work he/she can put inside a project.

Again, let’s take a backseat and appreciate/encourage all freshers like @Nickson to do a similar kind of work, by congratulating them

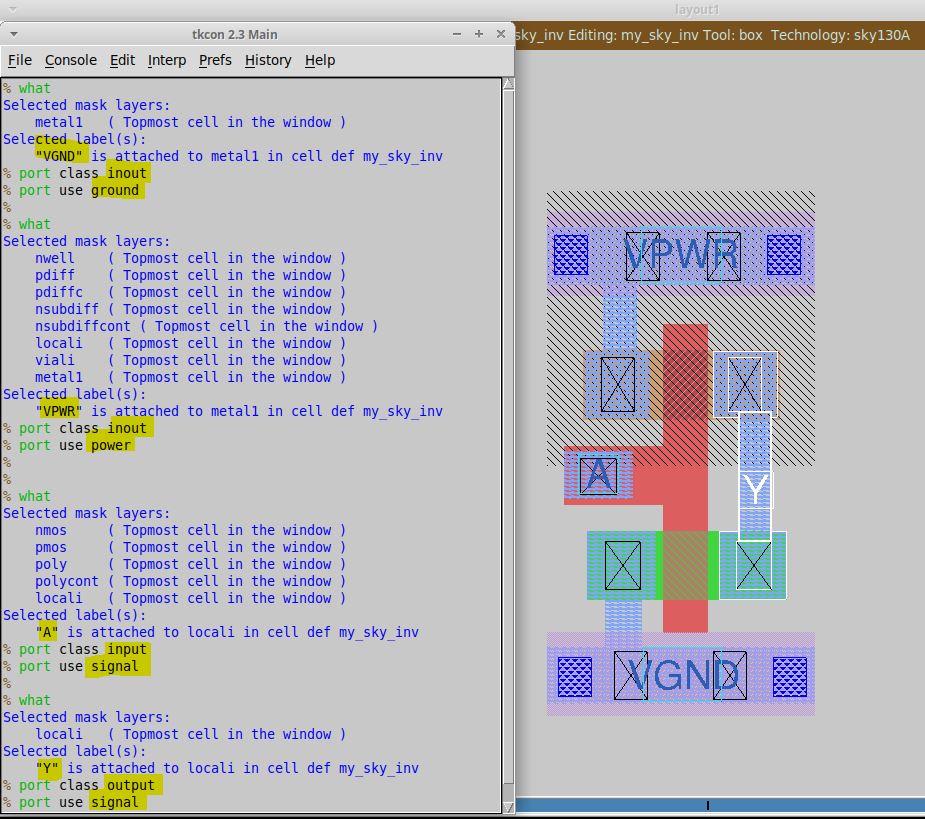

@Nickson joined our research project group under VSD Research internship program which runs for 8-weeks. He was supposed to develop flow for standard cell design and characterization using all open-source tools – magic/ngspice, then plug those standard cells into open-source PNR flow by open-lane, and benchmark RTL2GDS flow results. This needed a knowledge, not only of PNR, but device physics, custom layout, DRC/LVS and then (finally) Physical design/STA.

All of above using open-source RISC-V design (picorv32a) + open-source EDA tools (open-lane by efabless) + open-process (google+skywater130nm).

We still have one pending work (a major one) to characterize a simple inverter against all * PVT process corners*. And we are waiting for spice models to be released on public platform. Once its done, consider characterization also done. Really thankful to @mkk @Mohamed Shalan @Tim Edwards @Ahmed Ghazy for helping at every stage of this experiment. Amazing experiments and documentation done here

Here’s detailed masterpiece of his work. Its open for review/critics/feedback/comments/usage and everything