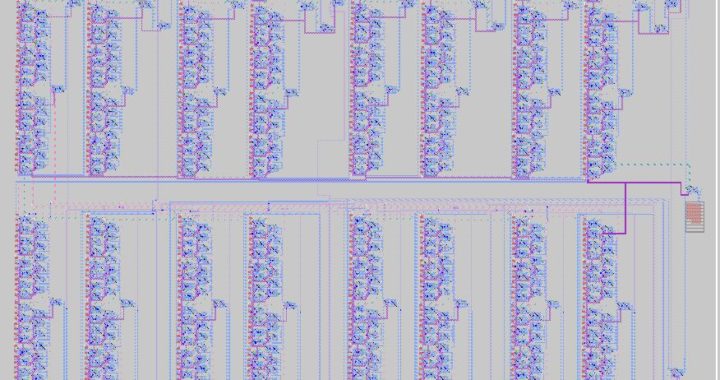

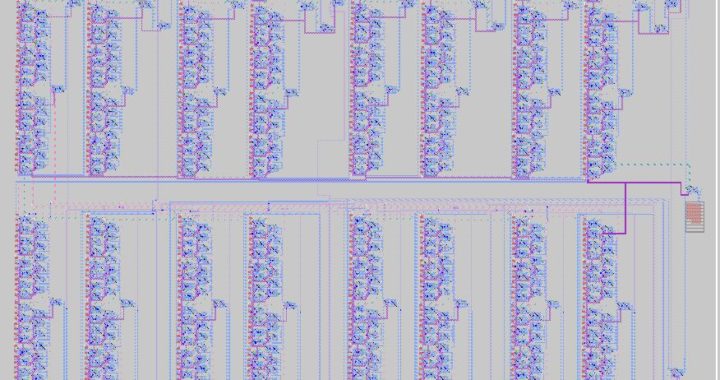

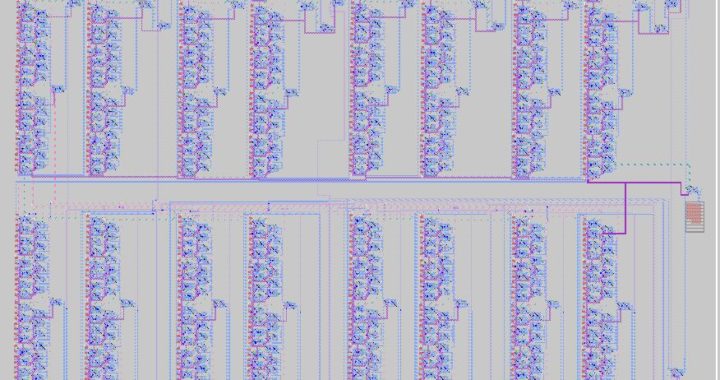

We have our 7th mile-stone in field of open-source analog IP design – 10-bit DAC using OSU180nm. If you observe his GitHub link, it will look not less than a professional one, and you would be surprised to know that this was built by 4th Year BTech student – @Ashutosh Sharma . It has a decent data-sheet also. Unbelievable!!

Ashutosh had joined our VSD Research IP design internship group 8-weeks back, along with 30 other interns. His journey on was from “I can’t, its too difficult” to “I did it“. Personally, only I know how hard it was for him when he saw an industry grade 10-bit DAC specifications on VSD IP website. We managed to achieve post-layout DNL of 3.5LSB and INL of 3.7LSB, which as per experience, is really tough for a fresher to achieve in a span of 8-weeks, but not impossible.

Its time all experienced people to take a back-seat (again) and congratulate @Ashutosh Sharma whole-heartedly, only for his dedication and never give-up nature. Its also time, that many VLSI freshers/pass-outs start looking at open-source problem statements in hardware domain and solve them. All of you are the future torch-bearers of VLSI open-source, and this is the right time to begin

Read below blog for more details and look at his GitHub link for a Masterpiece Art of Work:

Wait for some more analog IP blocks announcements. All the best and happy learning