Hi

As you must be knowing by now, about the RISC-V related upcoming courses, I would like to brief you about the entire range that we plan to cover in these course. And. Just like my another online course, this one’s going to be another masterpiece. Me and my team are working really hard to get this to you ASAP.

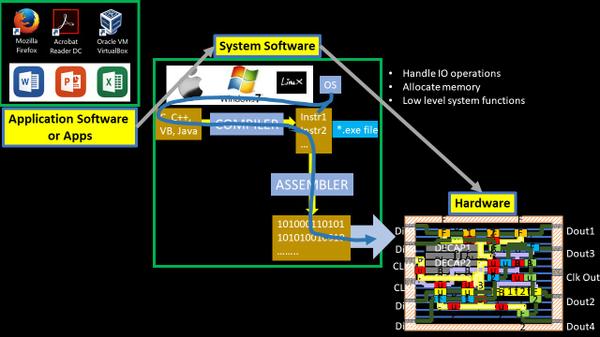

Think of any application program or app (as it’s called today). It has millions of lines of codes written in some high-level language. But at the end of the day, it needs to be run on a hardware or chip which is present inside your phones or laptops. So who does that translation? – a layer system software’s – let’s focus on 2 of them which we need – OS (operating system) and compiler. Below image shows the bridge – system software – placed in between application programs and hardware:

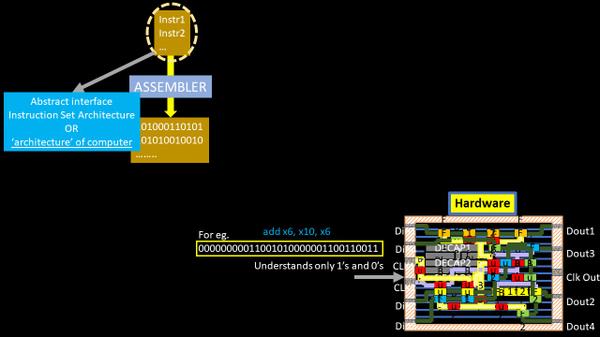

If you observe closely, hardware understands only 1’s and 0’s and, believe it or not, there was an era, when first programmers did communicate with computes using binary numbers. That’s tedious, right? Very quickly, some notations like add, sub, and many more were invented and they replaced binary numbers shown as below: Here the combination of binary numbers instruct the hardware to add numbers in registers x10 and x6, and place the result in x6

Just like this, there are hundreds of instruction sets being architected and the entire set of instructions are proprietary, like, ARM architecture for mobiles, x86 architecture for servers, and many more. Similarly, RISC-V is a new set of instructions, that is developed in Computer Science division of EECS department at University of California, Berkeley and now, it is all set to become standard open architecture for industries

Going a level below, once you define an architecture, you would need a CPU core (to being with, an RTL) that implements and understands RISC-V instructions. In simple terms, the hardware should process binary machine language of a RISC-V command like ‘add’ and store results in some register which will be further processed by an IO.

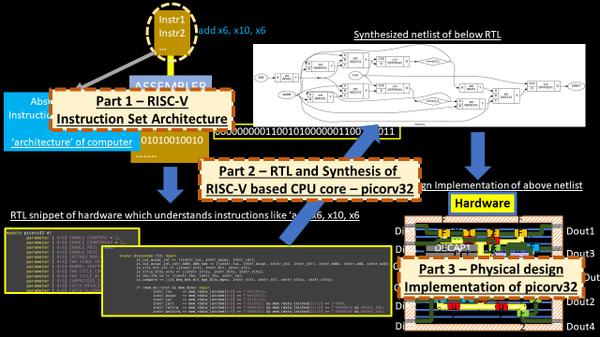

The above RTL then needs to be run through a PNR tool chain to produce the layout, ready for fabrication. The below image covers it all:

Hence, we divide our set of courses in 3 parts as shown below:

Sounds exciting – I mean, you will learn, understand and implement an entire processor – Isn’t that cool? Well, it is…I can’t wait to publish this courses for you. So stay tuned….