Get geared up for my next “to be” launched course on CCS timing libraries – Constructs and characterization. Let me be a bit frank here – If PNR and STA are ‘body’ of VLSI backend design, then “timing libraries” is the ‘soul’ of it.

To be a great backend engineer, you can’t skip in-depth knowledge of timing libraries, as complete PNR and STA depends on its contents. Some example of how important is it, can be seen, when your PNR tool tries to optimize placement for timing…that ‘timing’ is being calculated using libraries.

Another example, when your STA tool tries to implement or perform an ECO, it needs to know timing information of the new cells or modified cells. That ‘timing’ is being inferred from libraries

So, in general, your PNR and STA (body) is nothing without timing libraries (soul).

That brings me to my (pre-launch) announcement of my new course on CCS timing libraries, which is scheduled to be very soon (may be within a week or 2)

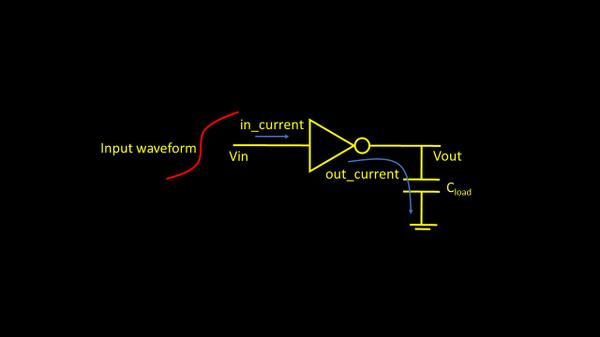

The concept…. it’s easy…look into the below image….

The first thing you need to be hands on is on SPICE…. Lots and lots of SPICE simulations….Now, once you become familiar with SPICE simulations (either you can learn it from my course on Circuit design and SPICE simulations OR you can use other references), it just a matter of providing the right input stimulus (input slew) and measuring output current for varying output load (Cload).

Now I am sure, there will be tons of questions, like why measure current at output and not voltage? Why vary input slew and output load? Etc….

You can research on that OR leave it my course, and your queries will be taken care of…. Why spend time (which you can’t get back) on things which can be easily out-sourced 🙂

Happy Learning !!