RISC-V enters India and VSD personally invite you…

Another chance, another medium, another platform for us to catch-up personally…. (You might want to forward this email to your colleagues staying close-by any one of below cities, and encourage them to attend this free event to learn more about RISC-V ecosystem in India)

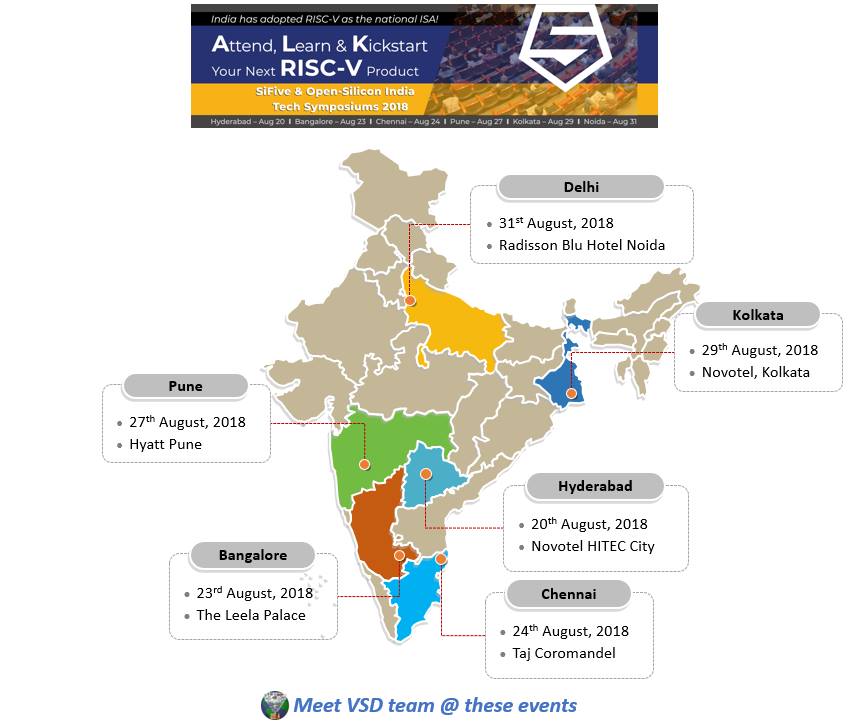

We would like to invite you to attend one of the SiFive & Open-Silicon Tech Symposiums taking place at six different locations throughout India in August. See map in below image for exact locations and date of events.

I would be presenting a very important tutorial, which closely connects open-source ISA implementation to open-source EDA tools – “How to design complex RISC-V SoC with open-source EDA tools and time to productize design ideas?”

Because India has adopted RISC-V as the national ISA, the time is now to learn from the academic luminaries who created this open architecture, and the engineers who are facilitating the mass adoption of RISC-V through customized silicon, design platforms and accelerators.

The seminar is free to attend and will include a broad spectrum of guest speakers, ranging from well-known professors at Indian institutes and research organizations to company founders and senior executives from the U.S. and India who are witnessing, first hand, the momentum of RISC-V and its impact on the worldwide semiconductor ecosystem.

All the best and happy learning…

——————————————————

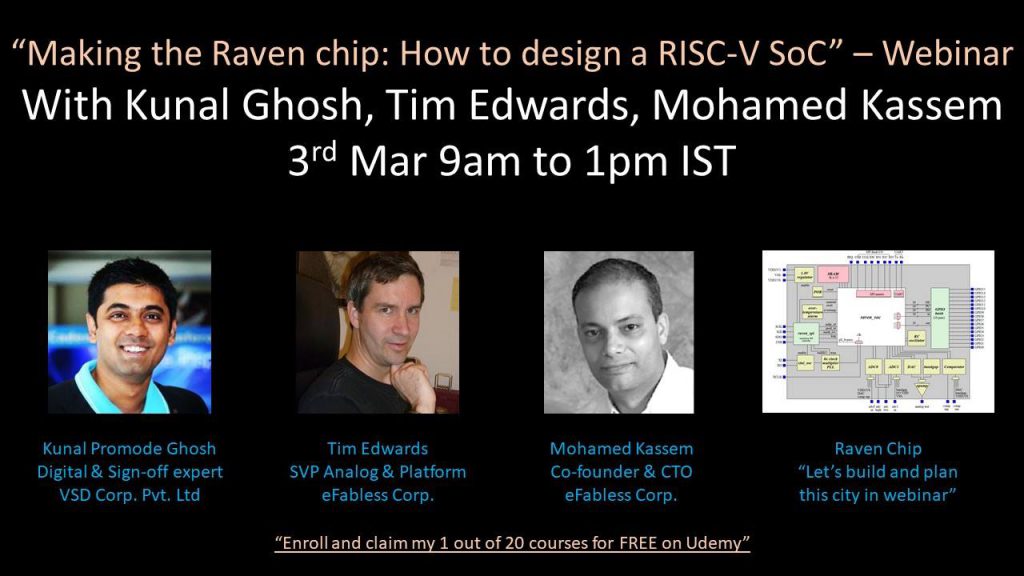

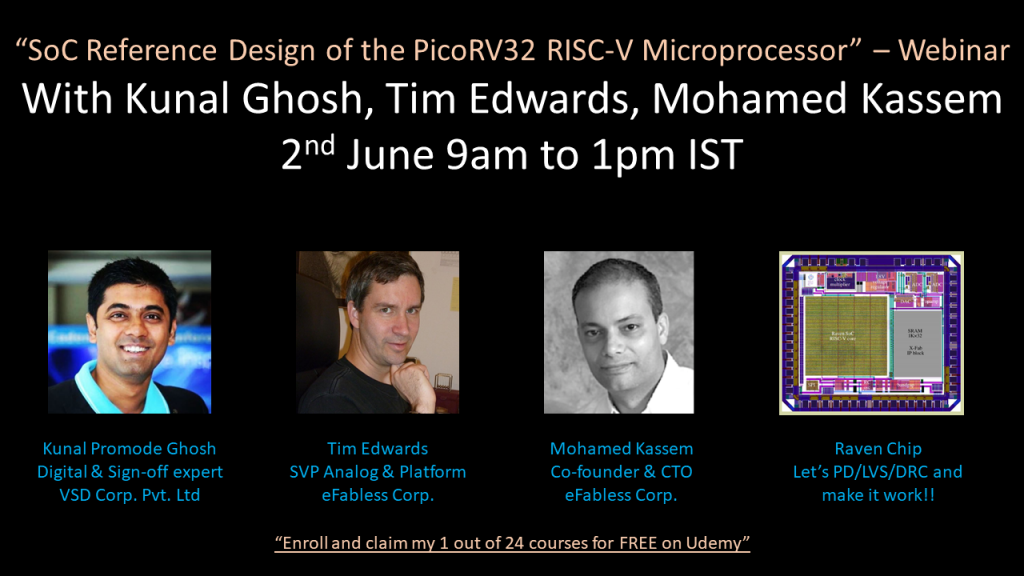

Webinar on “SoC Reference Design of the PicoRV32 RISC-V Microprocessor” – With Kunal Ghosh, Tim Edwards & Mohamed Kassem

After successful webinar on Making of Raven Chip, this time we take the chip forward and implement using end-to-end opensource EDA tools, and all on efabless cloud. What does this mean to us? It means, you can start innovating on a design, build RTL and do synth/PD/LVS/DRC all using opensource EDA framework and not pay a single penny for license.

The big question How is this possible?

Thereby, I welcome you all to my next (follow-up) webinar with Tim Edwards and Mohamed Kassem on 2nd June and below is the

Webinar Agenda:

Part 1: IP digital flow and chip integration on efabless.com

- The efabless model (recap from Part 1)

- The efabless platform:

- The (updated) Marketplace

- CloudV (continued work in progress)

- Open Galaxy (updated apps)

- The Raven chip project (update)

Part 2: Digital synthesis with CloudV

- The CloudV platform

- CloudV ongoing development

- Interactive CloudV tutorial:

- Clone an open-source “soft” IP

- Synthesis using CloudV

- Export to Open Galaxy

Part 3: Synthesis flow on Open Galaxy

- Synthesis

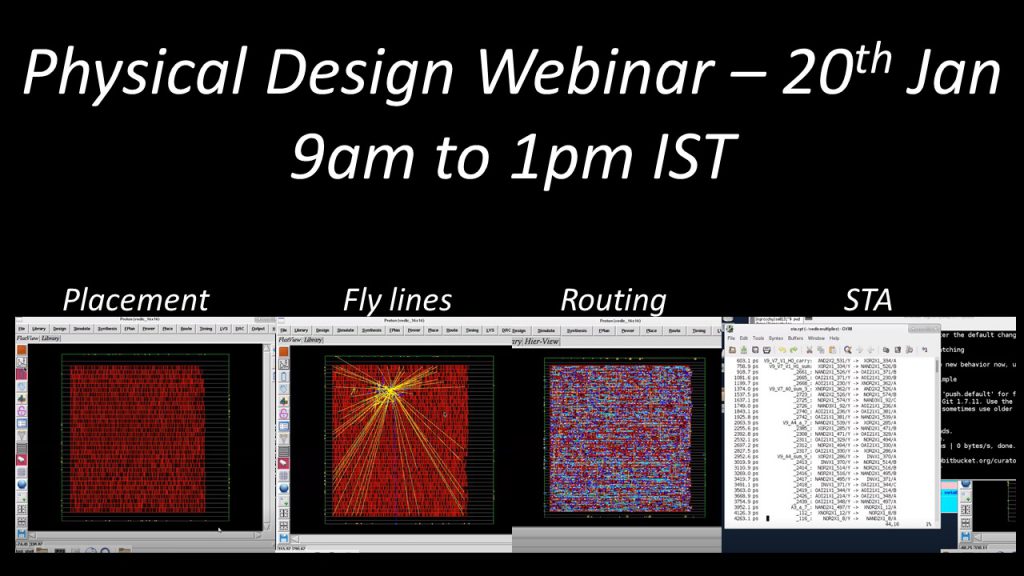

- Placement

- Routing

- DRC

- LVS

- Interactive tutorial:

- Clone the raven_spi IP block

- Run through “qflow” synthesis steps to layout

Part 4: Full chip integration on Open Galaxy

- Floorplanning the core

- Generating and connecting the padframe

- Placing components

- Top-level signal routing

- Top-level power routing

- Interactive tutorial: Using the layout tool for top-level integration

Tips and tricks for using the Magic VLSI layout tool efficiently

Part 5: Full-chip verification on Open Galaxy

- Additional requirements: Substrate contacts, antenna tie-downs, etc.

- Final DRC

- Final LVS

- Interactive tutorial: Using the LVS tool for top-level verification

Tips for understanding LVS errors and how to fix them

Part 6: Challenge

Design and verify a small chip in 0.18 m technology

Padframe provided

1.8V only (no voltage regulator), applied CMOS clock (no oscillator)

- Create a simple verilog function (details TBD)

- Synthesize, place, and route the digital block

- Compose top level from padframe and digital block

- Route core to pads

- Verify DRC and LVS

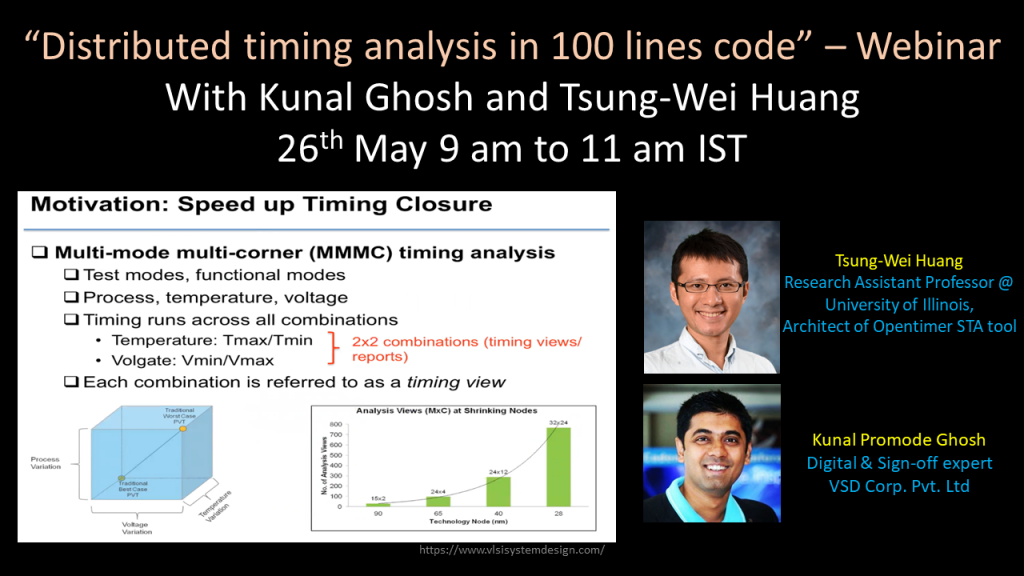

Webinar “Distributed timing analysis in 100 lines code” on 26th May 2018 by Tsung-Wei Huang

Recorded Version for people who missed it !!

VSD – SoC Design of the PicoRV32 RISCV micro-processor

————————————————————————————

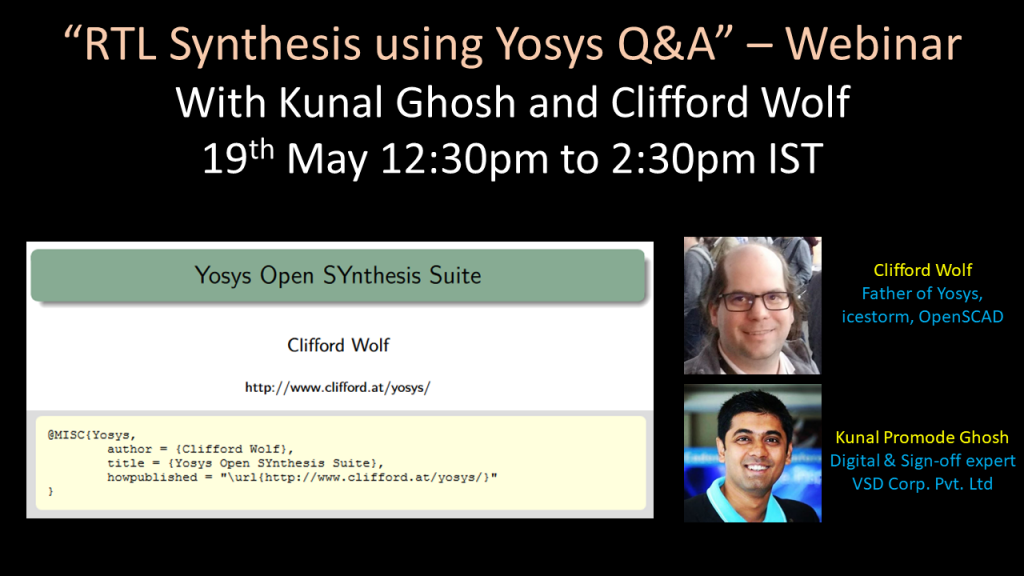

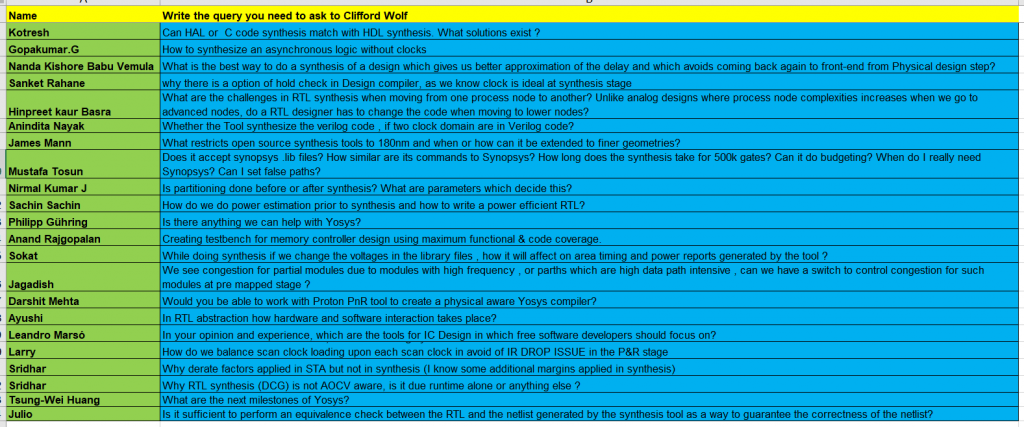

Note of Appreciation – I have worked with Clifford in my course on TCL programming Part 1 & 2, and really Thank him for all his guidance for making of TCL programming course.