Hey There,

If you think, 7 years is too much of time we spent building our company, think of below people who have spent more than 20+ years building what they love.

Very few people know, the company we started 7 years back, was just after my post-graduation at IIT Bombay. And the reason to start this journey, was to create a well-defined path for people to know the power of opensource EDA tools. Why? Because, we studied all our coursework at IIT Bombay using all open-source tools (except for projects which were sponsored)

A good thing about IIT Bombay, is we built lot of open-source tools and were a big fan of them. But something was missing – a guideline. There was no book, material, online content, video, absolutely nothing which demonstrated “how to use opensource tools in real chip tape-out”.

I really feel so sorry for people who approach me asking if I (can) teach using commercial EDA tools. Of-course I can. In fact anybody, with a year or two experience with these tools, can. But, what they can’t, and we can, is the approach to tackle any complex design irrespective of tool. Believe me, industry is looking for these kind of candidates

Let me give me you an example – You have an emergency and you need to rush to a hospital. Now you don’t have your favorite ‘xyz’ car with you, which you have driven for years and which you have expertise in. Does that mean, you will not use ‘abc’ car to go to hospital? If ‘abc’ car is broken, and if that’s the only car available, then you would learn how to quickly work-around ‘abc’ so that, it atleast takes you till the hospital. – This is what even VLSI industry is looking for and that’s how we were taught at IIT Bombay

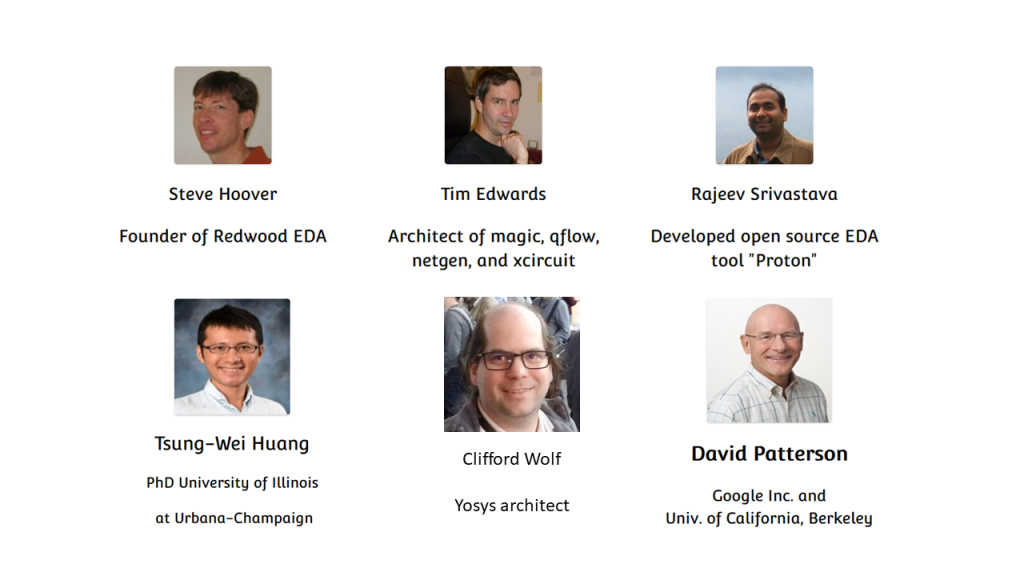

Since then, we have promoted courses using a lot of open-source EDA tools like Opentimer for STA, qflow for Physical design, TL-verilog for pipelining, Yosys for Synthesis, Proton for EDA and many more. Not only that, we have organized an online conference (as you might be aware) and here’s the link with details:

https://www.vlsisystemdesign.com/vsdopen2018-2/

And after DARPA’s announcement on investing in opensource tools and SiFive’s initiative to release RISC-V cores, I would love to bring up this video again, which we had created as a tribute to open-source EDA tools. This was made 2-3 years back:

I will also be presenting hierarchical PNR approach using opensource EDA tools at RISC-V workshop at Chennai, at IIT Madras. Below is the link to enroll

“Embrace the change and be a part of it…”

All the best and happy learning….