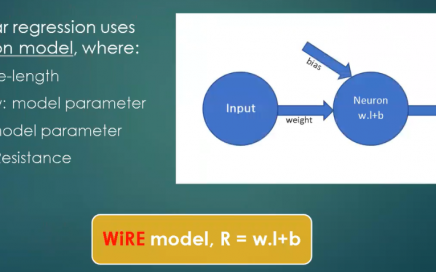

Symposium V – Machine Intelligence in EDA/CAD applications

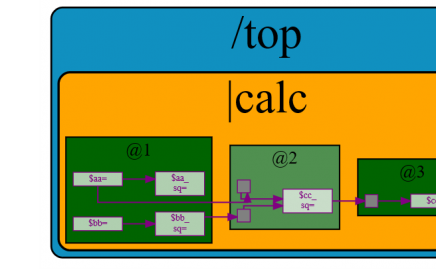

Symposium V – Machine Intelligence in EDA/CAD applications- Let’s investigate a simple Wire Resistance Estimate (WiRE) model

This is common design automation problem which is used for estimating timing and power characteristics for analysis and implementation for many steps in ASIC flow. We will restrict our scope to physical implementation only, where known quantity is “length” of wire and resistance is predicted.