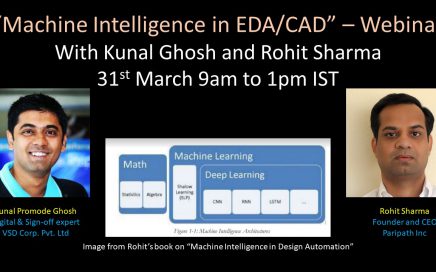

Machine learning contest: And the winner is….

Last week we conducted Machine Learning contest where participants were asked to modify loss function program to bring out best possible accuracy in terms of mean and sigma, by designing a new multinomial model. We have a winner and a special mention