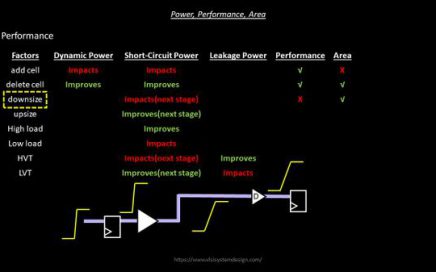

PPA (power, performance, area) card

A PPA card like the above, is something which every VLSI engineer should be carrying like a business card. Why? Right from RTL to synthesis to PNR to signoff, we do things like upsize, downsize, VT swap, and many more, and all these factors impacts or tweaks your design PPA in one way or the other.

Let’s take an example of ‘downsize’