Starting a career in static timing analysis domain, and now actively working on an opensource implementation fllow of RISC-V architecture, has been a journey. For last couple of months, I guess from around March this year, I was hooked to RISC-V buzz which was all over my Linkedin, my messages.

At that point of time, as me and my small team were working on preparing for an open-source conference, I was so focused on finishing what I had on my plate, that I completely ignored the buzz. Result – we had an awesome conference back there in England. Point to be taken – Starve your distractions, feed your focus

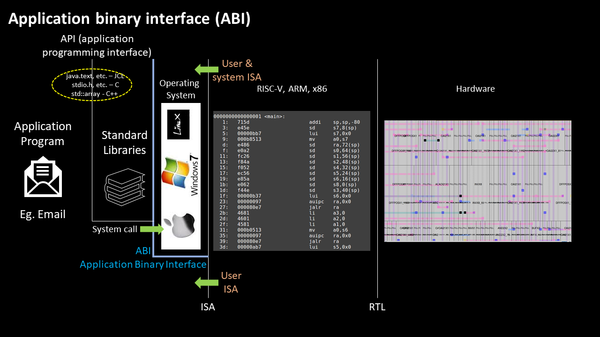

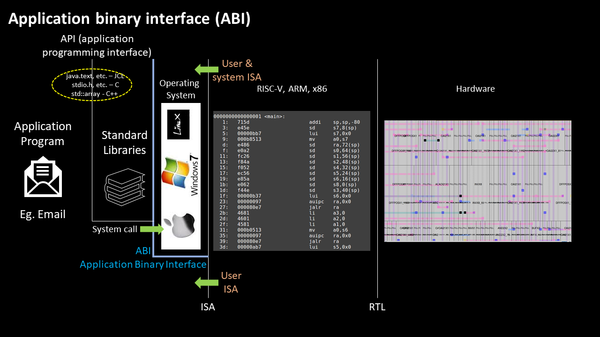

Nevertheless, after I finished one, it was time to get hooked to new topic, opensource RISC-V instruction set architecture. When looking at it from a business perspective, it was the coolest shift you could ever see in the VLSI and semi-conductor industry. But this perspective is not what my students were looking for. They (and me too) were looking forward to understanding a bit more about this architecture.

Solution – Be a student as long as you still have something to learn and this will mean all your life

That shift in attitude helped, and I got to interact with the pioneers of RISC-V – Prof. David Patterson. All of you, who have done a bit of research about RISC-V, must have known him. For others, David Patterson is the Pardee Professor of Computer Science, Emeritus at the University of California at Berkeley, which he joined after graduating from UCLA in 1977.