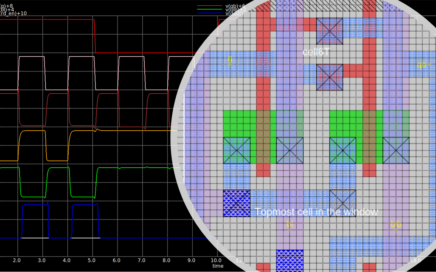

3rd mile-stone in 1-week in field of open-source – 4kB SRAM design

@Yash joined our research project group under VSD Research internship program which runs for 8-weeks. He was supposed to explore openRAM memory compiler flow, develop all custom cells required by openRAM using OSU180nm and generate 4kB SRAM with an access time of 2.5ns