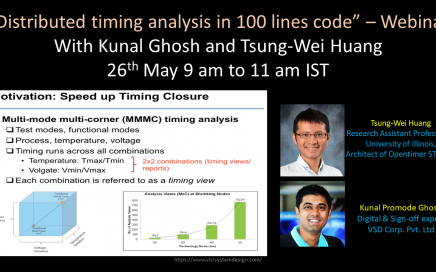

VSDOpen 2018 Keynote 3: Applying Open community Innovation to hardware Product creation

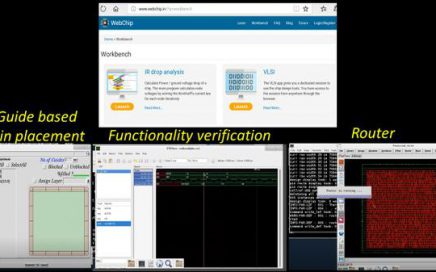

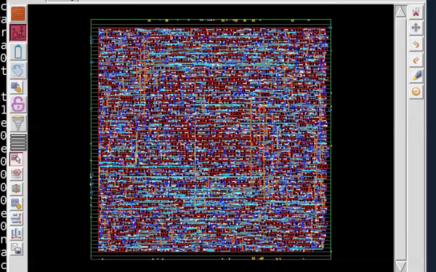

Mohamed Kassem is the CTO and Co-Founder of efabless.com, the first semiconductor company applying open community innovation to all aspects of product development. Prior to launching efablesshe […]