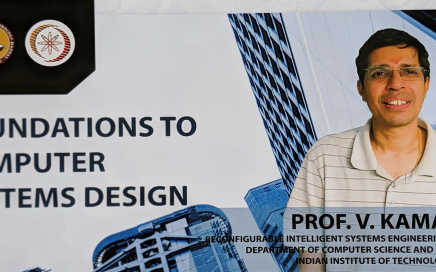

After SHAKTI processor, another master-stroke by Prof. V. Kamakoti

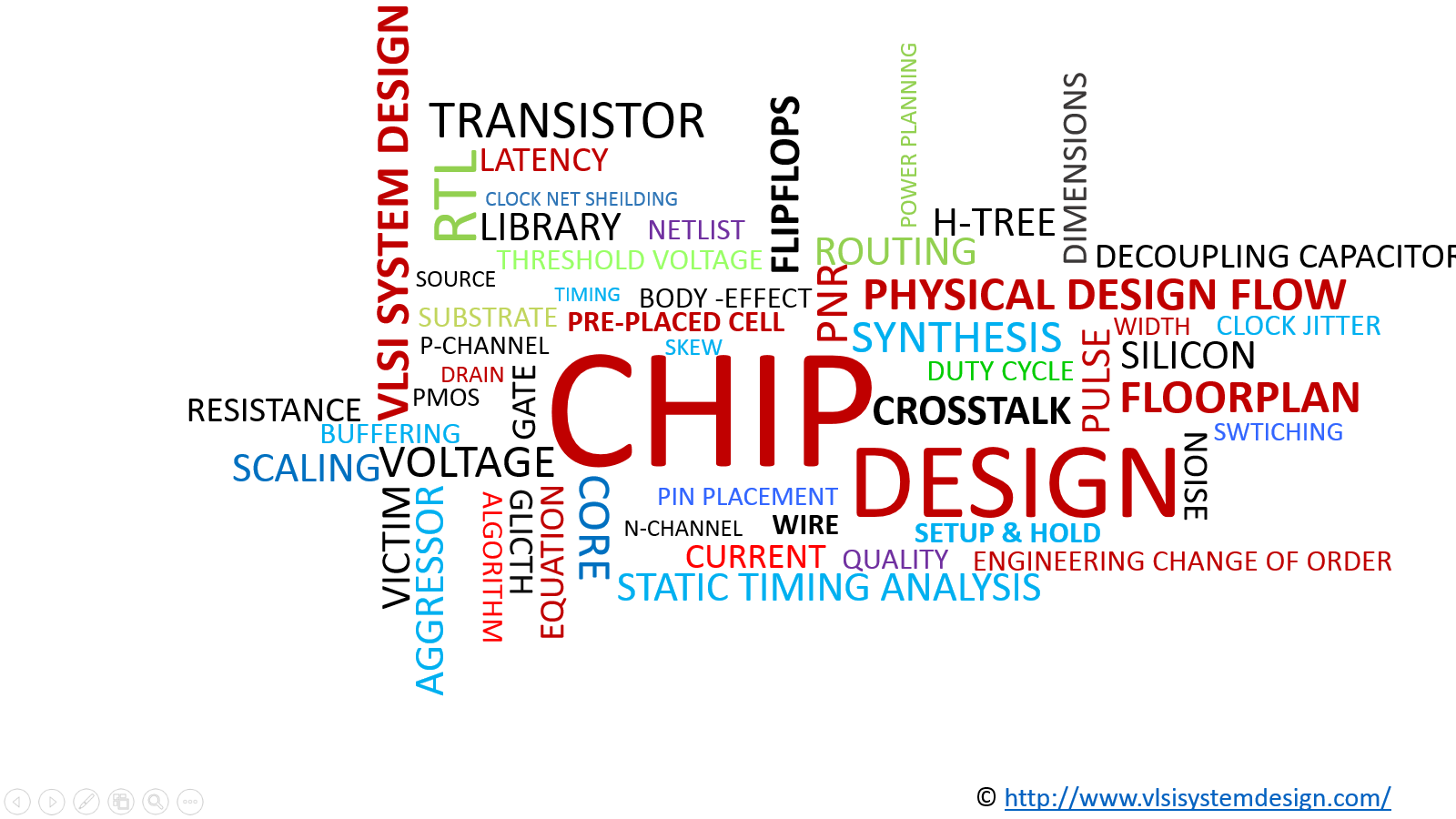

Online university Course name – Foundation of Computer Systems Design

This course is being taught by Prof. V. Kamakoti, who needs no introduction, who lead India’s first RISC-V microprocessor SHAKTI teamand made all of us proud.