VSDOpen announces new technologies for effective VLSI skill development-2

If you have been following VSDOpen for the last 5-years, the theme has been maintained – What VSD did last year and what VSD will do next year

If you have been following VSDOpen for the last 5-years, the theme has been maintained – What VSD did last year and what VSD will do next year

VSDOpen conference is an attempt to bring out some cutting-edge activities especially around open-source EDA with a special focus on skill development using open and proprietary tools. VSDOpen also focuses on milestones achieved by VSD in the past year, and some interesting projects which VSD will be working on in the next year. It’s like the VSD Annual Hands-on meeting where everyone is invited for free and allowed to rate us for our work 🙂

Join us to explore such concepts and more, where we use Python to leverage its library-rich environment feasible for verification using Vyoma’s UpTickPro platform, in this edition of Capture the Bug hackathon, organized by NIELIT, Calicut, mentored by IIT Madras, in association with VLSI System Design and Vyoma Systems.

Hackathon details – https://nielithackathon.in/

For the upcoming Capture The Bug Hackathon, participant is free to choose any Verilog Open Source design from any website/reference similar to that of OpenCores with appropriate licensing which is compatible with Icarus Verilog and also the Verilog code needs to be synthesizable.

Happy Verification!!!

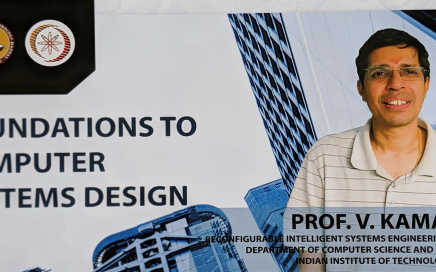

Online university Course name – Foundation of Computer Systems Design

This course is being taught by Prof. V. Kamakoti, who needs no introduction, who lead India’s first RISC-V microprocessor SHAKTI teamand made all of us proud.

With learning being online, SHAKTI core and ‘vsdflow’ being opensource, this is first-time in the history of VLSI design & EDA (thanks to RISC-V ecosystem and Shakti Team at IITM lead by Prof. Kamakoti), a chip will ever be taped-out using all open source flow, which will cater to almost 80% Indian Semiconductor Market.