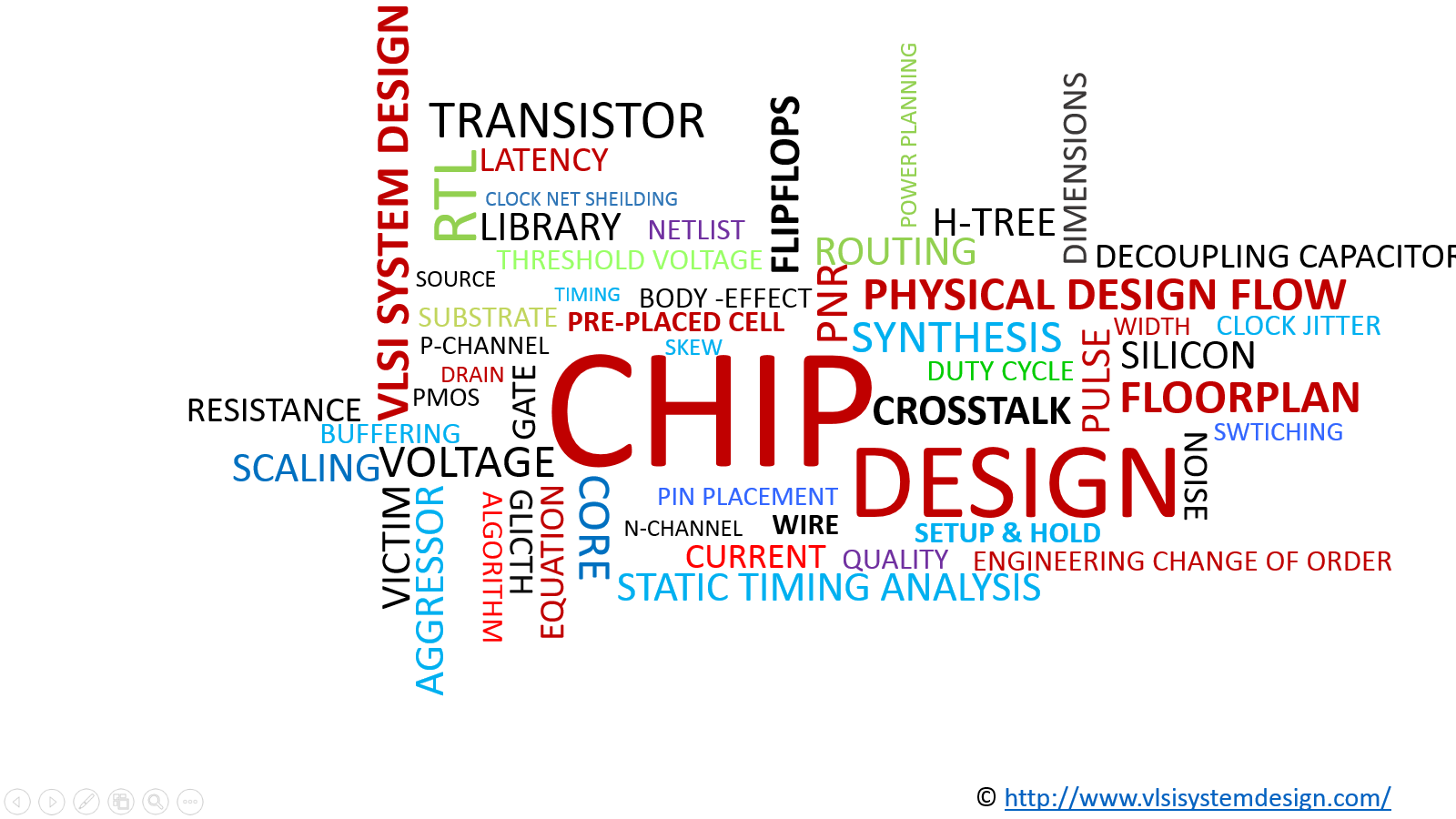

VSD aims to tackle global chip designer shortage

Above article does talk about chip shortage, which is due to increased demand of consumer electronics like laptops, tablets, mobiles, which was never the case […]

Above article does talk about chip shortage, which is due to increased demand of consumer electronics like laptops, tablets, mobiles, which was never the case […]

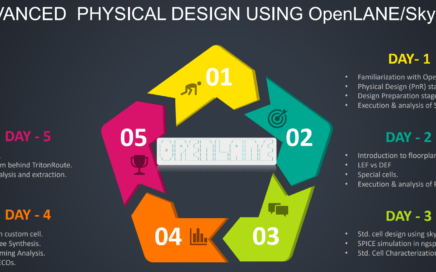

Know what Pentagon is? It is a plane figure which has 5-straight sides and 5-angles. For a perfect pentagon, it needs all its sides and angles to be the same, till the last decimal. Do you know what is the similarity between pentagon and our upcoming workshop “Advanced Physical Design workshop using OpenLANE/SKY130”? Look above image and you would guess it right. It is a perfect blend of topics where even a fresher can jump-start his/her career in chip design in just 5-days

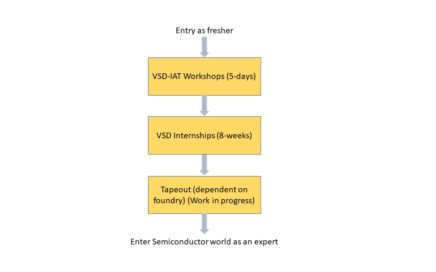

A great one – not only for VSD, but also for entire VSD community. The journey has just begun, in nutshell, below image shows a well-designed VLSI Skilling model (VSD Workshops + VSD-IP design Internship + Tapeout[working on it]), which is not just participants driven but also silicon proven. To summarize, given a problem statement, VSD Interns and participants, who have gone through this rigorous training and designing model will have much better ways to figure out solutions by themselves.

And that’s where VSD must play an especially important role to bring in latest and greatest VLSI skills to you, atleast in the field of open-source hardware. VSD owes a lot to VLSI community and hence has planned 3 exclusive cloud lab-based VLSI workshops on 3 important topics, with top 3 expert instructors from around globe, having more than 2 decades of experience – Tim Edwards, Steve Hoover, and Prof. Mohamed Shalan

Open-source EDA tool development with lab exercises using Sky130 pdk’s by Google/Skywater

RISC-V micro-architecture using transaction level – Verilog with lab exercises on Makerchip Platform

SoC and Physical Design using Automated RTL2GDS OpenLANE tool with lab exercises using demo design and Sky130 pdk’s.

Ashutosh had joined our VSD Research IP design internship group 8-weeks back, along with 30 other interns. His journey on was from “I can’t, its too difficult” to “I did it”. Personally, only I know how hard it was for him when he saw an industry grade 10-bit DAC specifications on VSD IP website. We managed to achieve post-layout DNL of 3.5LSB and INL of 3.7LSB, which as per experience, is really tough for a fresher to achieve in a span of 8-weeks, but not impossible.

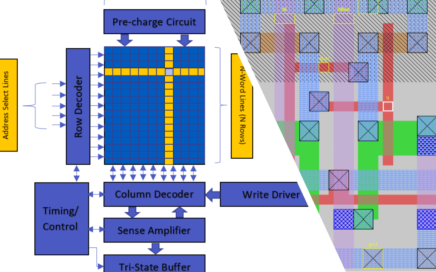

This time its @Reuel did a pretty great job of building a pretty compact 6T-SRAM cell and he is just a third year engineering student

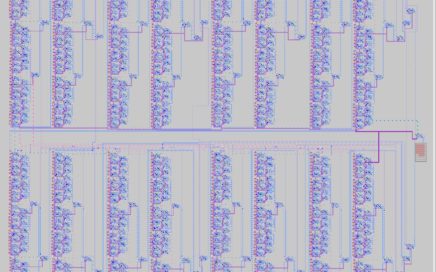

We had Makerchip IDE, TL-Verilog, Day wise Slack channels, Classroom GitHub and VSD-IAT – All of them so seamlessly integrated that every participant followed the loop and there you go. Out of 110 participants, 35 participants built entire basic RISC-V CPU core which is close to 30% participants, and all in 5-days

to build the shell script for ‘vsdflow’ on CentOS, and finally I have the first cut ready. You just need to follow steps given in below link for CentOS, and all opensource EDA tools (PNR, STA, Layout, LVS) will be installed on your system. There are 2 testcases (picorv32 and spi_slave) inside the below link to test whether all tools have been installed or not. After running the shell script in below link, you need run the testcase

So, I took up two STA tools, OpenSTA from openroad project and “——-” from “——-“, to explain, to some extent, what “bench-marking” means to me. I would also encourage everyone reading this blog to come up with their definitions of “bench-marks” for other tools and we can model that. You can fill-up “——” with one of your favorite industry grade EDA tools. The concept of benchmark won’t change

Hi Vlsi

Your feedback has been continuously pushing us to the edge. And I really want to Thank You for all the support you have been giving over the past. Its due to this push, we are now releasing (especially for VLSI freshers), a package, which you just need to download/run. That would install all opensource EDA tools on your UNIX machine plus run a complete RTL-2-GDS on RISC-V core ‘picorv32’.

All you need to do is go to below github link, and follow simple 5 steps given in the README of below link: