We all know timing analysis is a really important task in overall chip design flow and its so complex and difficult task. The chip that we incorporate today has billions of transistors, resulting timing analysis runtime is tool large. Also, we need to analyze timing under different conditions, so its not just a single run that you get a final result.

While there are several solutions to mitigate this computation issue, the problem is most of the work is architecturally constrained by single machine. And as design complexity continue to grow larger and larger, we have to add more and more CPU and memories to the machine, but not very cost-efficient

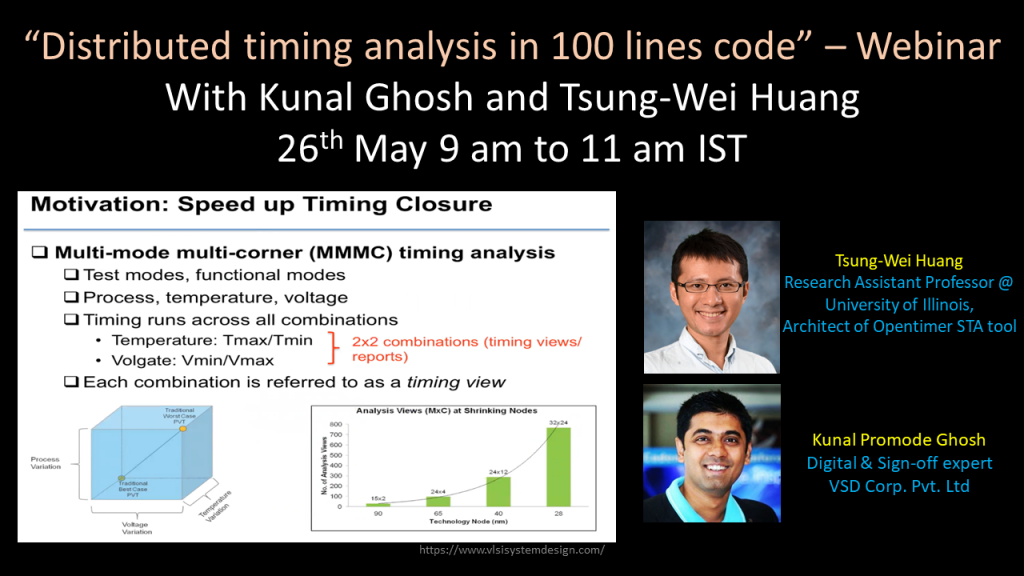

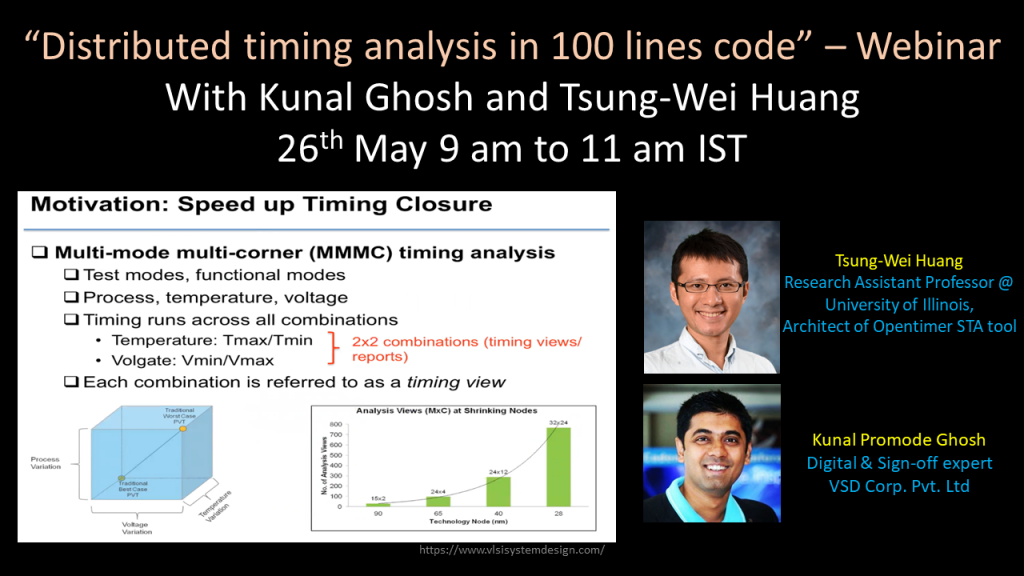

There are multiple places, we can introduce distributed computing to timing and major motivation is to speed up the timing closure. We have to analyze timing under different range of conditions, typically quantified as modes (test mode, functional mode) and corner (PVT). The number of combinations (timing views) you have to run is typically increasing exponentially with lower nodes. That’s where you need to need to distribute timing analysis across different machines.

So let’s distribute it and do it within 100lines of code using DTCraft – A High-performance cluster computing engine. Welcome to the webinar on “Distributed timing analysis within 100 lines of code” on 26th May, 9am IST (Limited Tickets). In my last webinar, all tickets sold out in 2 days, so you might want to reserve your seat TODAY. Here’s the link:

Tsung-Wei Huang:

Tsung-Wei Huang is Research Assistant Professor, in Department of Electrical and Computer Engineering at University of Illinois at Urbana-Champaign, IL, USA. He has done his PhD in Electrical and Computer Engineering at UIUC. He holds 2 patents and more than 30 Conference and Journal Paper publications