Hello

For those who have been in sync with my course on Static timing analysis, will already know this topic very well. For those who haven’t, donot worry. This is the perfect blog for you. And also, this will make you realize how different and exclusive our course on STA is

What we know is, we model jitter as ‘clock uncertainty’. The question (that everyone is keen to know), who decides jitter or uncertainty value. Well, there is physics behind this, and (donot worry) we will not go into much details, but in brief

This is where an eye diagram is really helpful. Stay with me and I will conclude what an eye diagram is, why is it called an ‘eye’ diagram and how do we get ‘jitter’ values

To begin with, look into the below flop clock pin. It expects 2 versions of clock signal (say for eg.) – the real one and the inverted one:

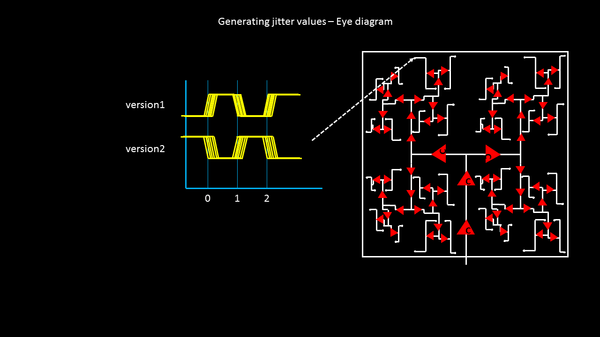

Now by just overlapping the equivalent edges of these waveforms, we can get a basic ‘eye’ for them as below

But, in reality, (considering silicon surface variation), the clock, which is supposed to arrive at ‘t’ ns, might not always arrive at ‘t’ns, but at t+x or t-x or t+2x, etc. You can think of silicon surface as a ‘road’, and distance from the clock port to any flop clock pin is ‘say’ 1mile. It’s not always possible for a car to cover 1 mile always at same time. Same thing is with clock edge as well.

Below is how the clock edge arrival varies at flop clock pin. (look at both version of clock below):

And this is how the resulting ‘eye’ looks like