Looking for a RISC-V processor design? You would find one on GitHub within seconds

You can build it too in upcoming RISC-V based MYTH workshop which has been approved by toughest critics in industry

RISC-V is one of the hottest buzzwords in the semiconductor industry. One might wonder why people are talking about a new ISA (Instruction Set Architecture) when the concept is decades old.

ISA is the set of specifications that define a processor’s fundamental model, not necessarily restricting the system’s microarchitecture.

RISC-V & RISC-V International Logo

Prof. David Patterson coined the term RISC (Reduced Instruction Set Computing), which has evolved into the present-day ARM, MIPS, and RISC-V. RISC-V started as a Berkeley project in 2010. It has gained interest from academia and industry alike for its open, modular, minimal, extensible, and royalty-free nature. Unlike others, RISC-V is free to use even in commercial applications.

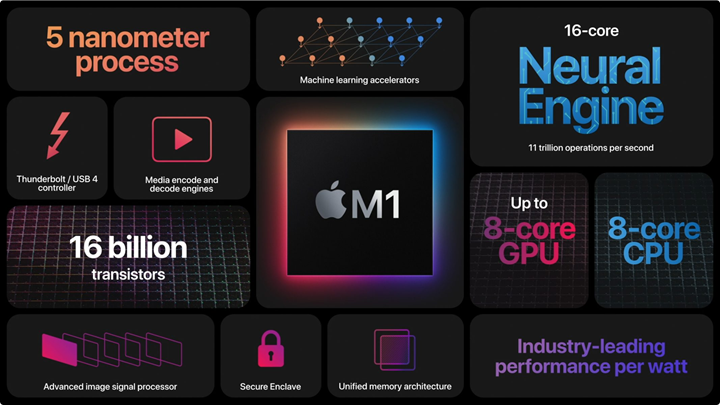

Apple Silicon to which Apple recently announced a switch is also based on RISC-based (ARM) Architecture. Desktop-grade RISC-V is also reaching mass production soon!

It supports 32/64/128 bit* implementations. The instructions are divided into modular extensions such as integer (I), floating-point (F), vector (V), etc., with the base RV32I implementation needing only 47 instructions.

It offers vacant encoding space, allowing users to implement their ISA-extensions independently. For, e.g., PULP (ETH Zurich) has one tuned for machine-learning applications.

This nature lowers the entry barrier (in affordability and access) for startups and students and opens up avenues for innovation in terms of architecture and methodologies for all.

Many prominent RISC-V implementations such as RocketChip (Chisel, UCB), SweRV (SystemVerilog, WD), PULP Platform (SystemVerilog, ETHZ), WARP-V(TL-Verilog, Redwood EDA), and VexRiscv (SpinalHDL) are free and open-source. Surprisingly, all having diverse microarchitecture and even different design languages.

What can be more delightful for a student than finding the RTL for an entire system on chip with modern architectural features on GitHub!!

And thanks to its open nature, you can implement your own too!!

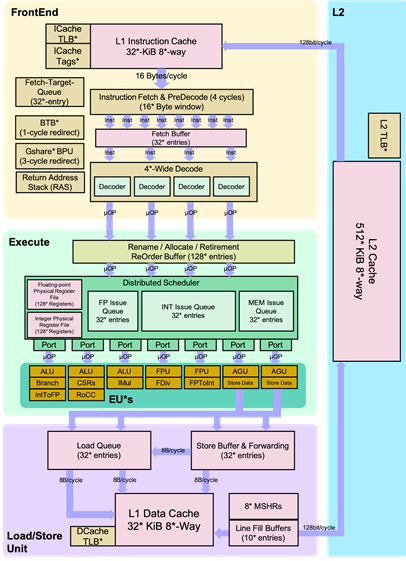

Detailed pipeline of the Berkeley Out-of-Order Machine (BOOM). (OoO RISC-V Implementation) (Also on GitHub!)

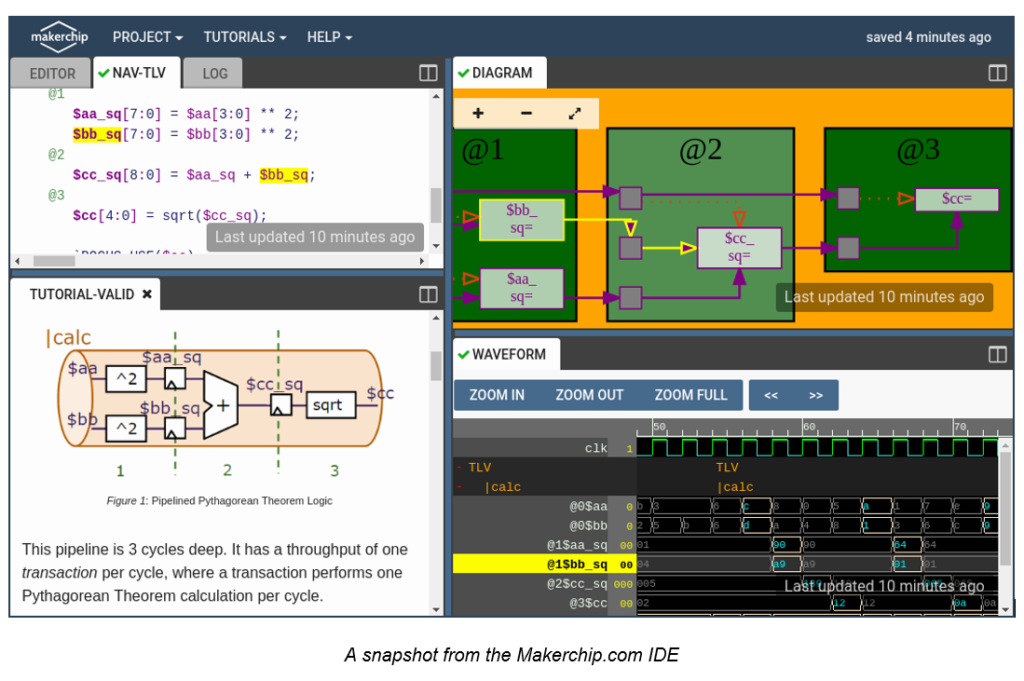

Among these, TL-Verilog (Transaction-Level), in particular, is a novel approach to digital design. It models systems with a timing-abstract, parameterizable, flexible, easy-to-learn/debug/document nature and significant code size reduction. It is neither HLS nor a programming language generating hardware but a modern abstraction close to the hardware.

All this can be used with Makerchip.com, a free IDE for TL-Verilog that supports the design, debugging, simulation, and visualization in a browser tab! SandPiper, the compiler for TL-Verilog, translates it to synthesizable (System)Verilog compatible with open-source and industry-proven design flows.

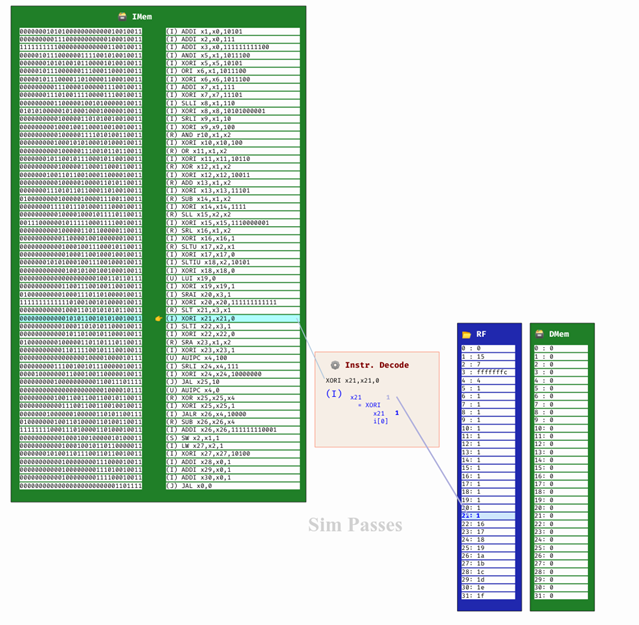

A snapshot from the VIZ (Visual Debug) example from Makerchip.com. This is a RISC-V CPU core in action.

The logic and simulation is linked to javascript functions which show the visualisation is real time.

Along with cutting down design time and efforts in the industry, this is great for students to gain hands-on experience. More than 250 students from the RISC-V MYTH Workshop went from introduction to ISA to designing a pipelined RISC-V implementation in just five days!

RISC-V and open-source hardware is undoubtedly destined to change the industry. Not just for the ISA and design, there are ongoing efforts to tape out an actual chip with completely open-source tools!

Join the revolution!

Author: Shivam Potdar is currently a Research Intern at CAD Lab, Indian Institute of Science (IISc) Bengaluru and pursuing final semester of B. Tech (EEE) from National Institute of Technology Karnataka (NITK), Surathkal. He has been a Teaching Assistant (TA) since the first iteration of the RISC-V MYTH Workshop by VSD and Redwood EDA.

Related Posts:

- Shape Tomorrow’s Technology Today: ELCIA Hackathon…

- Accelerating the Future of Semiconductor Talent with…

- The Future of Chip Design: The Next Generation is…

- Bluetooth automated smart access

- PARKinSENSE

- COLORIMETER

- Secure Saiyan

- Home safety system

- RISC-V Mini Game Console

- Water level monitoring and control in water tank