Hello

Today, I was a guest speaker at one of the biggest Technical Conference held in Bangalore, and luckily I met few people who had read my previous post. This is what I call “From Virtuality to Reality“. Its really awesome feeling, when you get to meet people personally.

We were identifying sources of variations, and below is the second one

2) Oxide Thickness

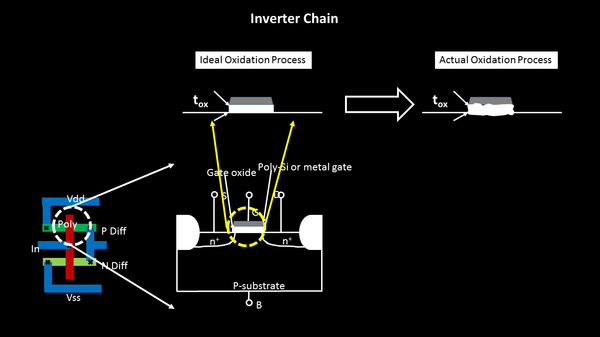

Let’s go back to the inverter layout and look which part are we talking about

Here, we are talking about gate oxide thickness variation

Below is the section from inverter chain, which we are worried about

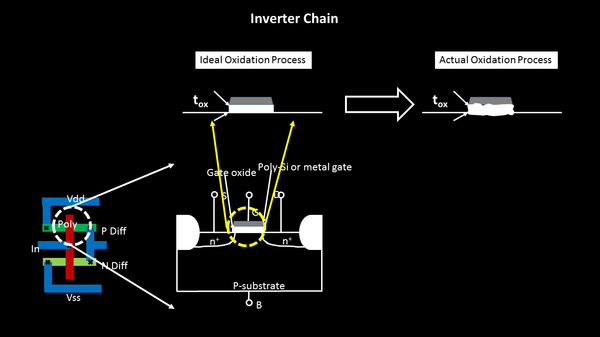

If we go by ideal fabrication process, below is what you will achieve, a perfectly cubic shape (below is the 2D image, so it looks rectangle) oxide layer, and perfectly deposited metal gate or poly-silicon gate

But, if we go by actual oxidation process, its very difficult or almost impossible to achieve the above perfect oxide thickness. And I can confidently say that, as I have worked on fabrication for a brief period of time during my Masters at IIT Bombay.

Below is what you will actually get

So, what’s wrong having above oxide thickness. Again, its the drain current (which is a function of oxide thickness, shown in below image) that will get varied for the complete chain of inverter, especially, the one’s on the sides. The variations in middle inverters will still be uniform. We discussed the reason for this in last post

Imagine a chain of, as long as, 40 inverters or buffers ….. the variation is HUGE. And this needs to be accounted for, in STA.

So the challenge is, how to we find the range and effectively model it in STA. Are we scared ? Ofcourse Not …. 🙂

“Be thankful for each new challenge, because it will build your strength and character.”Author Unknown :),Be Thankful

Thanks

Kunal