The “RISC-V based MYTH (Microprocessor for You in Thirty Hours)” workshop provides a structured introduction to RISC-V architecture, covering software-to-hardware concepts through hands-on labs. Participants begin with C programming, GCC compilation, and Spike simulation before progressing to number systems and assembly programming. The workshop delves into combinational and sequential logic, pipeline implementation, and microarchitecture of a single-cycle RISC-V CPU. Labs include instruction decoding, register file operations, ALU implementation, and control flow hazards. The final stages focus on load-store instructions, memory management, and CPU testbench development, offering comprehensive learning experience in microprocessor design and verification.

The “RISC-V based MYTH (Microprocessor for You in Thirty Hours)” workshop introduces participants to RISC-V architecture, guiding them from software concepts to hardware implementation. It begins with C programming, where learners write and compile simple programs using the RISC-V GCC toolchain. They explore disassembly, simulation with Spike, and debugging techniques. The workshop then covers number systems, explaining signed and unsigned 64-bit representations, crucial for understanding processor arithmetic. These foundational concepts prepare participants for low-level programming and hardware interactions.

Next, the workshop dives into Application Binary Interface (ABI), memory allocation, and assembly-level instruction handling. Participants learn about the 32 general-purpose registers in RISC-V and implement basic operations like load, store, and arithmetic instructions. Function calls and stack management introduce execution flow control. Learners then explore combinational and sequential logic using Makerchip, designing logic gates, multiplexers, and arithmetic circuits. These concepts provide a deeper understanding of how software translates into hardware functionality in microprocessor design.

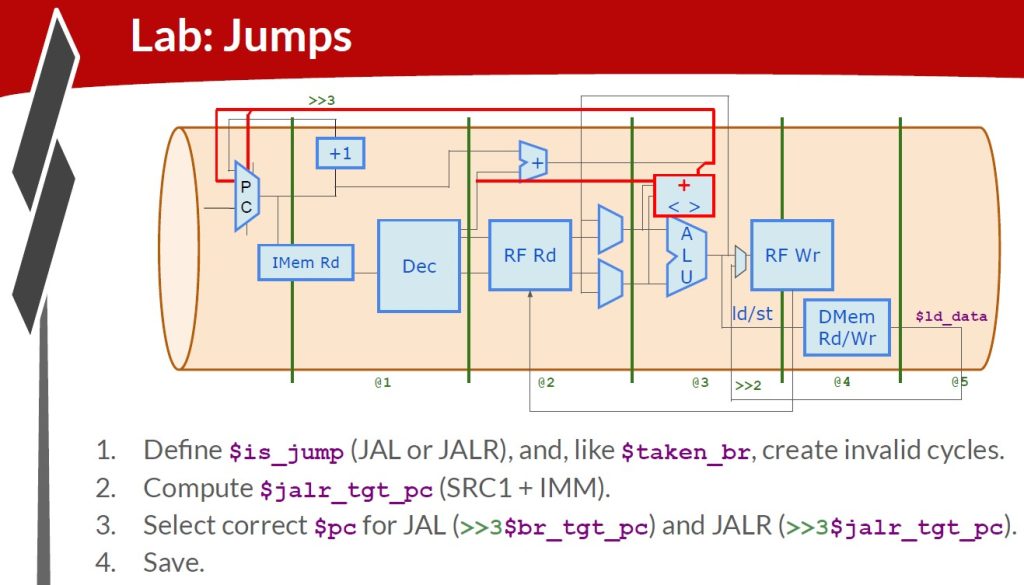

The workshop then shifts to processor pipeline implementation and microarchitecture. Participants design a single-cycle RISC-V CPU, implementing instruction fetch, decode, and execution stages. Through hands-on labs, they optimize instruction flow, address pipeline hazards, and implement branching mechanisms. Error detection and correction techniques are introduced, ensuring accurate computation. Testing and debugging strategies help participants validate their processor designs, preparing them for real-world challenges in microprocessor development.

In the final phase, learners explore advanced microarchitectural optimizations, including control flow hazards, instruction dependencies, and memory management techniques. They refine instruction execution paths, optimize ALU operations, and implement load-store mechanisms. By the end, participants gain a strong foundation in RISC-V design, having built and optimized their own processor core. This hands-on experience prepares them for careers in semiconductor design, embedded systems, and computer architecture.

Project : Participants may choose one of the following projects to the design:

Seize this hands-on learning opportunity to master microprocessor design!

Meet Your Guides to the World of VLSI Design

Steve Hoover, founder of Redwood EDA, Steve is fostering an open-source silicon ecosystem through numerous technologies including the WARP-V CPU core generator with support for RISC-V. His main focus is design methodology and tools enabled by Transaction-Level Verilog (TL-Verilog), available to all at makerchip.com. He is also the lead developer of the 1st CLaaS open-source framework for cloud FPGAs. Steve holds a BS in electrical engineering summa cum laude from Rensselaer Polytechnic Institute and an MS in computer science from the University of Illinois. He has designed numerous components for high-performance server CPUs and network architectures for DEC, Compaq, and Intel.

Kunal Ghosh, the visionary co-founder of VLSI System Design (VSD) Corp. Pvt. Ltd., stands at the forefront of online open-source EDA and hardware design education, particularly in the realm of RISC-V.

With a portfolio of 50 top-tier VLSI online courses, Kunal has enriched the learning journey of over 90,000 students across 153 countries. His expertise extends beyond training; he’s actively involved in pioneering open-source projects and design collaborations with esteemed institutions like IIT Madras, IIT Bombay, IIT Guwahati and IIT Hyderabad.

His current focus is on crafting high-quality open-source Analog/Digital IPs, a groundbreaking endeavor in open-source hardware design. Kunal’s rich industry experience includes roles at Qualcomm and Cadence, specializing in SoC design. He holds a master’s degree from IIT Bombay, where he specialized in VLSI & Nano-electronics, with a focus on sub-100nm Electron Beam Lithography Optimization techniques.

Teaching Assistant

Shrihari is a Digital Design Engineer who focuses on the architecture and micro-architecture of energy-efficient ML accelerators. He earned his MS from the University of Texas at Austin, where he is currently pursuing a PhD. His research interests include edge ML accelerator architectures, low-power heterogeneous systems, and workload-based power management. He is also an active contributor to the TL-Verilog ecosystem, collaborating with Redwood EDA to develop open-source tools that simplify hardware design.

Yes, also you will be provided roughly 24x7 live support from mentors in various time zones over the duration of the workshop. We use Slack for live chat support and do also take up daily sync-up and one-to-one calls, as necessary.

We welcome interested participants from all stages of their career. Even if you have learned logic design and CPU microarchitecture in the past, this course offers a modern perspective. TL-Verilog is a new and emerging standard and is useful for industry and academia alike. Get involved in revolutionizing your design/teaching/learning process!

This course teaches the basics of digital logic in the context of a modern design approach. So newcomers will learn something just as well as experienced designers. We have received positive feedback from learners ranging from 12 years of age to industry veterans, though we suggest this course for college age and above for folks on a technical path.

The main tool used in the workshop is the Makerchip.com online IDE, which is public and always open for development of open-source designs. You will also be given lifetime access to the slides and lab files after the workshop.

No. Labs will be done on VSD-IAT cloud platform and Makerchip.com online IDE. You will be given access in your browser to a Linux Terminal, which has all necessary tools installed. Post workshop, we will provide scripts and templates to install or use the tools on your personal systems.

TL-Verilog (Transaction-Level Verilog) is a new and emerging standard supporting “timing abstract” digital design, without which this course would not be possible. In addition to its powerful modeling constructs, it also eliminates legacy complexities of Verilog such as regs and wires, generate blocks, blocking vs. non blocking etc. It provides clean semantics that are easy to learn whether you already know Verilog or not. It integrates with existing commercial and open-source EDA tools by generating synthesizable (System)Verilog.

Learn more at https://www.redwoodeda.com/tl-verilog

If you are not able to join workshop, last date to apply for refund in 5th Feb 2025, 11:59 PM IST

Burn RISC-V core on VSDSquadronFPGA Mini

+

Offer Price

VSD, standing as a trailblazing Semiconductor EdTech company and a community-based Technology Aggregator, is revolutionizing the landscape of VLSI Design. With the belief that “Creativity is just connecting things”, VSD has mastered the art of linking the right resources with the community. This unique approach has sparked a significant transformation in the VLSI Design process.

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Job Roles, Convergence With Embedded Systems, and Startups

VSD showcased at Semicon India 2023

VSDSquadron Educational board on Tamil News channel

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Karnataka VLSI roadshow at Sahyadri College, Mangalore