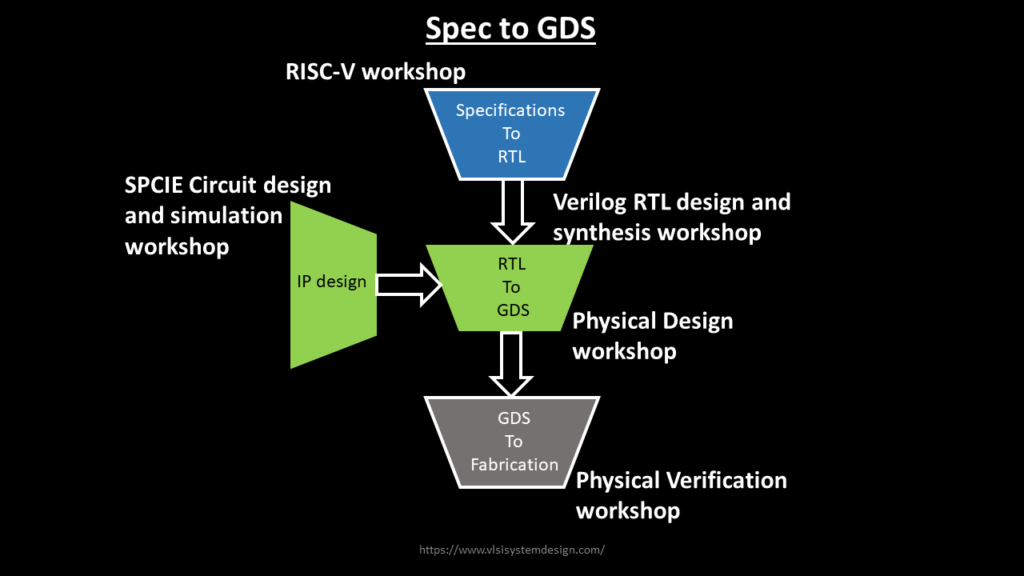

You might have seen the above image in one form or another, in different our blogs or VSD websites. Every trapezoid in above image is a field or career in itself and each one of them has immense job and innovation opportunities. Infact, chip design is like real estate - it's ever green and never-ending. AI based EDA automation will quadruple the number of chips which will be manufactured in the next decade. Automation would need engineers to think differently, out-of-the-box and work on problem statements which were never encountered before and work fast within a certain time limit.

That's what VSD workshops prepare you for - deadline based design oriented workshops. Though, VSD has multiple courses which gives lifetime access and which is good if you want to revise fundamentals. But if you are looking to prepare yourselves for future challenges, VSD time-bound workshops are the ones you should be going for. Participants who have completed VSD-time bound workshops with a valid lab based reports, are now in top semiconductor companies all over world working in cutting edge technologies like EDA automation, neural networks, multicore processors and complex analog IP design

The question is, which workshop should be taken at what stage? Look at the above image and let me break it down below -

1) First Workshop - RISC-V based MYTH (Microprocessor for You in Thirty Hours)

Any electronic device (for eg., calculator) takes the right shape once you write specifications of that device. These specifications are then converted into proto-RTL (high level RTL in human language) and verified against specifications. Now, VSD could have taken the calculator directly as a starting point for specification, but that would have been too easy as the calculator would need just a simple ALU. So we took a processor which can be used for calculator application and various others as well (like waveform generator for eg.). And hence that's the first workshop that should be taken. We are using RISC-V based processor and hence the workshop name is RISC-V based MYTH (Microprocessors for You in Thirty Hours)

2) Second Workshop - RTL design and synthesis using Sky130

Once we have a proto-RTL, it's time to convert the RTL into digital logic gates (AND, OR, XOR, Flip Flops). But that would be as easy as running a simple 'synth' command. We would love all of you to build good RTL and not just RTL, which is what differentiates an engineer from a good engineer. This phase would need you to think logically and supply the right RTL to the synthesis engine so it produces what you want it to produce, that consumes optimum power, takes optimum area and provides high performance. These would need a surgical analysis of RTL and that's where you should go for RTL design and synthesis using Sky130 workshop. Why sky130? Why not the latest technology like 28nm or 7nm? Of-course, we can and we will be. But currently 130 nm is the only industry grade manufacturable libraries which is available as open-source

3) Third Workshop - Circuit design and SPICE simulations using Sky130

Before we jump into Physical design/STA workshops, it's very important to know your foundry well. Like in a restaurant, you are well aware of what you are ordering, so that you have a rough idea about the taste of it, similarly, since you will be placing an order with the foundry, it's better to know what you will be receiving once the chip arrives. Just like taste is for food, inverter characteristics is for foundry. If we are able to characterize the robustness of the inverter which is provided by the foundry by characterizing the inverter against a range of stimulus, you can estimate performance of your final chip. We can do that at Circuit design and SPICE simulation using Sky130 workshop. Why Sky130? Same reason. It's available openly for us to characterize

4) Fourth Workshop - SoC/Physical design using Sky130

Ideally, we would want to call this workshop as SoC design rather than Physical design. Physical design is one of the steps in SoC design. But physical design is being branded around very well in industry, so let's call it physical design for time-being. If your interviewer is really good and knows what he is asking, then the moment you say "SoC design" rather than "Physical Design", you will catch his attention. Now to find out what is the similarity/differences between the both and do a "good" physical design rather than "just" physical design, go ahead and enroll for a Physical design workshop using OpenLANE and Sky130.

5) Fifth Workshop - Physical Verification using Sky130

Finally, once you are done with Physical design, it's time to hand-off your design to Skywater foundry for manufacturing. For that, there are certain advanced sign-off checks with metals and base layers visible. Ideally, this should have been an automated thing where GDS produced should be DRC/LVS free. To confirm if this really is the case, we need to run certain checks and we need to do this fast. Physical verification using Sky130 workshop explains such smart techniques from basics to advanced, and these checks are similar to what you would be doing using commercial tools

Very important - Note all the workshop dates before enrolling as some of them or most of them will be on the same dates. So enroll only for any one and then you can enroll for the others later. Try to identify which is your strongest area in the above 5-workshops, and which one needs work. Enroll for that workshop only and we will take care of the rest during the 5-day duration of the workshop

All the best and happy learning

Related Posts:

- Accelerating the Future of Semiconductor Talent with…

- Making a Game Console Using VSDSquadron Mini

- Real Time Implementation of BitNetMCU

- Advanced Easy to use Burgler Alarm

- Water level monitoring and control in water tank

- Bluetooth automated smart access

- Secure Saiyan

- Home safety system

- Shape Tomorrow’s Technology Today: ELCIA Hackathon…

- Smart Plant Care using the VSD_Squadron-MINI-BOARD