This blog is regarding abstract submission for VSDOpen2018, which is the first online conference in VLSI, that covers all aspects of semiconductor technology with prime focus to build SoC using RISC-V CPU by illustrating exciting ways using (only) c.

This conference has 6 symposium, out of which fourth symposium is to come up with innovative ways of place and route to achieve best PPA. List of other symposium and session chair can be found in below link:

https://www.vlsisystemdesign.com/vsdopen2018-2/

This blog is about Symposium IV – Place and route of digital IC’s for best PPA (abstract submission last date is 15th August, please see above link for details)

Now we have demonstrated in our courses and webinars, about various ways of doing physical design. Let’s say you have RISC-V implementation for which you need to PNR. There are multiple ways of flows which we can use to achieve the best PPA.

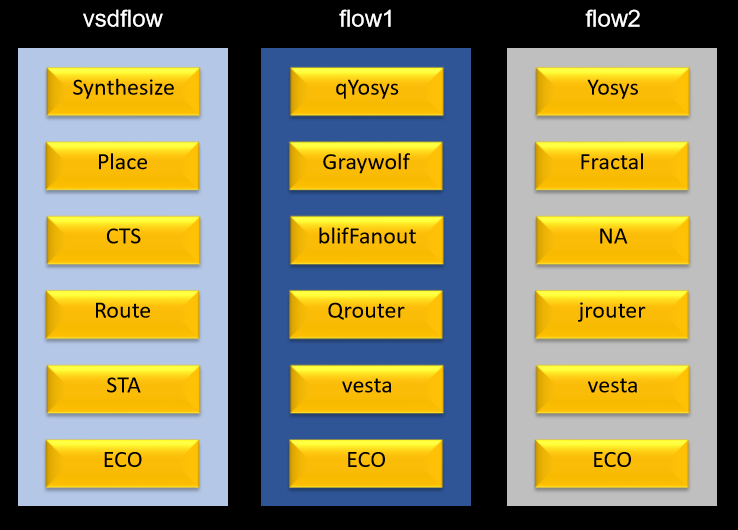

For eg. below case shows an example of 2 flows.

Flow 1 uses a set of below tools:

Synthesize – qYosys

Placement – Graywolf

CTS – blifFanout

Route – Qrouter

STA – vesta

While flow 2 uses set of below tools:

Synthesize – Yosys

Placement – Fractal

CTS – (Proton in-built)

Route – Jrouter

STA – vesta

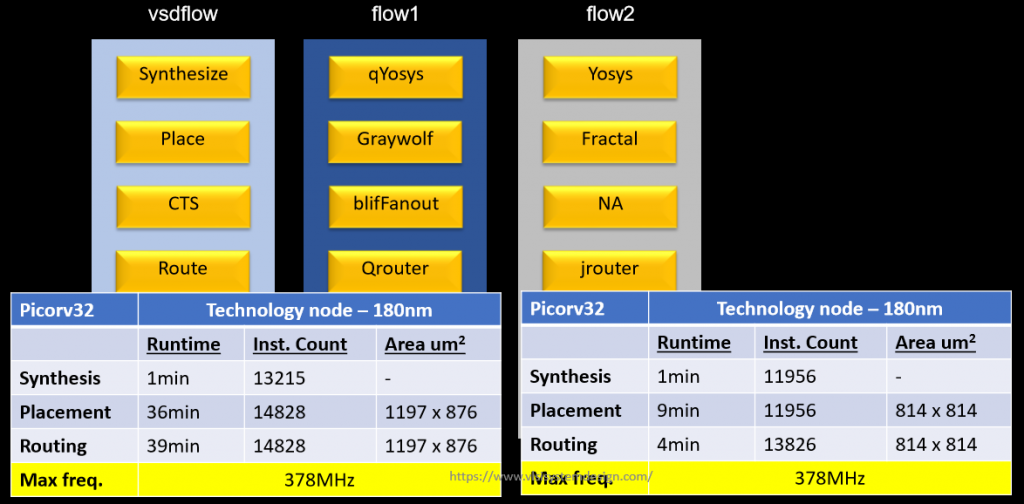

There are good chances that both the above flows will give 2 different PPA’s as shown below:

Left one being from “Flow 1” and right one for “Flow 2”

An important point to note, though the post-layout frequency seems to be same for both flows (due to the fact that it’s a small design), the instance count and runtimes for both flows is significantly different. For “flow 1”, which uses all open-source tools, the instance count is about 15k, and whole runtime about 80min, whereas “flow 2” which uses partially open-source and partially paid tools, the instance count is about 12k with whole runtime being just 15min

A good takeaway from above is which is the best flow – Well, there is no single answer to this. You can use “flow 1”, if your organization is constrained by cost and comparable performance, and you can go for “flow 2” if performance is the criteria.

Now, we have 2 below courses which shows how to do PNR, with different platforms.

Flow 1-

https://www.udemy.com/vsd-soc-design-of-the-picorv32-riscv-micro-processor/

Flow 2-

https://www.udemy.com/vsd-physical-design-webinar-using-eda-tool-proton/

Think of an idea to use a mix-n-match of both platforms and come up with a flow for best performance and area. Submit your idea to VSDOpen online conference using below link:

https://www.vlsisystemdesign.com/abstract-submission/

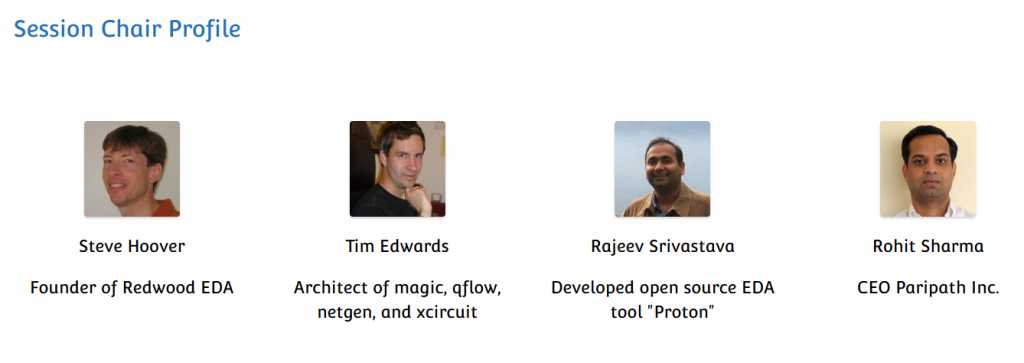

All your ideas will be reviewed by below panel of session chairs (who are all experts in their domains) and you might just get a chance to showcase your innovation to top crowd from VLSI industries:

The reason for this conference is to do out-of-the-box things in field of VLSI, to showcase your versatility and talent to a lot of TOP people, and get their attention, all online.

“This can be your new creative resume”

All the best for your submissions and happy learning