History etched with VSDOpen2018 – First VLSI online conference….

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

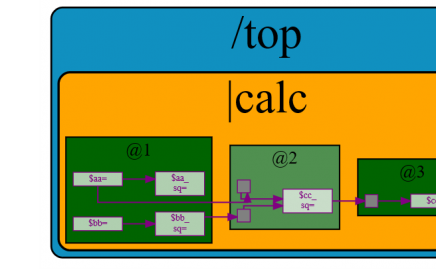

Transaction-Level Verilog (TL-Verilog) is an emerging extension to SystemVerilog that supports transaction-level design methodology. In transaction-level design, a transaction is an entity that moves through a microarchitecture. It is operated upon and steered through the machinery by flow components such as pipelines, arbiters, and queues. A transaction might be a machine instruction, a flit of a packet, or a memory read/write. The flow of a transaction can be established independently from the logic that operates on the transaction. We present a preliminary library of TL-Verilog flow components that can be quickly stitched together to establish a complete microarchitecture. We show how transaction logic, like packet decoding, can be added within this flow.

This paper introduces TL-V erilog and W ARP-V and then describes the formal verification of WARP-V using riscv-formal, a formal verification framework for RISC-V. Timing-abstraction and transaction-level design are showing significant benefits for hardware modeling, but this is the first demonstration of their benefits for verification modeling. As evidence of these benefits, the verification of all RISC-V configurations of WARP-V is accomplished in a single page of code.

Question – Who doesn’t want a 3.5X improvement in their code size? I guess everyone wants efficient and effective improvement. Now these are just few tips to have the easy implementation of pipe-line. You are free to implement your ideas in TL-verilog, compile, simulate and see the improvements on your own. For few more tips, you might want to check out below course on “VSD – Pipelining RISC-

V with TL-verilog”