Open Source Hardware Journey Begins !!

A dream and a mission statement that was framed 10 years back by VSD and Efabless (or let us say, e-fabulous) has now taken a surprisingly good shape and IS FINALLY SILICON PROVEN. Release of Google/Skywater-130nm open PDK’s was really the final piece of entire VLSI training model puzzle.

Find all repository at

Bidirectional Counter

Pankaj Agrawal

GitHub

Synchronous First In First Out for Memory Storage and Processing

Anmol Shetty

GitHub

Universal Asynchronous Receiver Transmitter Protocol based Hardware Transmitter

Jay shah

GitHub

Universal Shift Register

Rakshit Bhatia

GitHub

Vending Machine with Change System

Siddhant Nayak

GitHub

Car Parking System

Ishan Desai

GitHub

Parallel input Serial output Shift register

Raj Kachhadiya

GitHub

8 bit BCD counter

Sritam Birtia

GitHub

Johnson counter

Aman Prajapati

GitHub

8-bit Gray code counter

Tejas B N

GitHub

Linear feedback shift register

Ritesh Lalwani

GitHub

Traffic Light Controller

Lokesh Maji

GitHub

LIFO (Last in First out) Buffer

Yash Kothari

GitHub

Three Bit Ring Counter

Arsh Kedia

GitHub

Baud Rate Generator

Rohit Raj

GitHub

PWM (Pulse width modulation) Generator

Himanshu Rai

GitHub

Serial In Parallel Out Shift Register

Aditya Singh

GitHub

Elevator Controller

Nishit Chechani

GitHub

Bidirectional up/down counter

Ujjawal Sharma

GitHub

4 Bit Bidirectional Counter

Sahil Mahajan

GitHub

ASIC design of automatic washing machine

Archan Desai

GitHub

Sequence Detection using Moore FSM

Anshul Mdurwar

GitHub

Sequence Detector 1010 (Without Overlapping) using Mealy Finite State Machine

Anuj Kumar Jha

GitHub

Parking Ticket Vending Machine

Suysh Mishra

GitHub

Parallel in parallel out shift register

Priyanshu

GitHub

Arithmatic Logic Unit

Aashish Tiwary

GitHub

Sequence detector_moore_machine (1011)

G.Ravi Kiran Reddy

GitHub

Pulse Width Modulated Wave Generator with Variable Duty Cycle

Sanampudi Gopala Krishna Reddy

GitHub

RISC-V

Vinay Rayapati

GitHub

Ring Counter

Kavya Agarwal

GitHub

Clock Gating

Vasanthi D R

GitHub

Frequency Divider

Dantu Nandini Devi

GitHub

Real-time clock

Banda Anusha

GitHub

Universal shift register

Debangana Mukherjee

GitHub

101011 Sequence detector _Mealy_Machine

Ajay Kumar

GitHub

PISO shift register

Mahati Basavaraju

GitHub

Ring counter

Ramya S

GitHub

Radix-2 4-Bit Booth’s Multiplier

Yashwant

GitHub

VSD, standing as a trailblazing Semiconductor EdTech company and a community-based Technology Aggregator, is revolutionizing the landscape of VLSI Design. With the belief that “Creativity is just connecting things”, VSD has mastered the art of linking the right resources with the community. This unique approach has sparked a significant transformation in the VLSI Design process.

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Job Roles, Convergence With Embedded Systems, and Startups

VSD showcased at Semicon India 2023

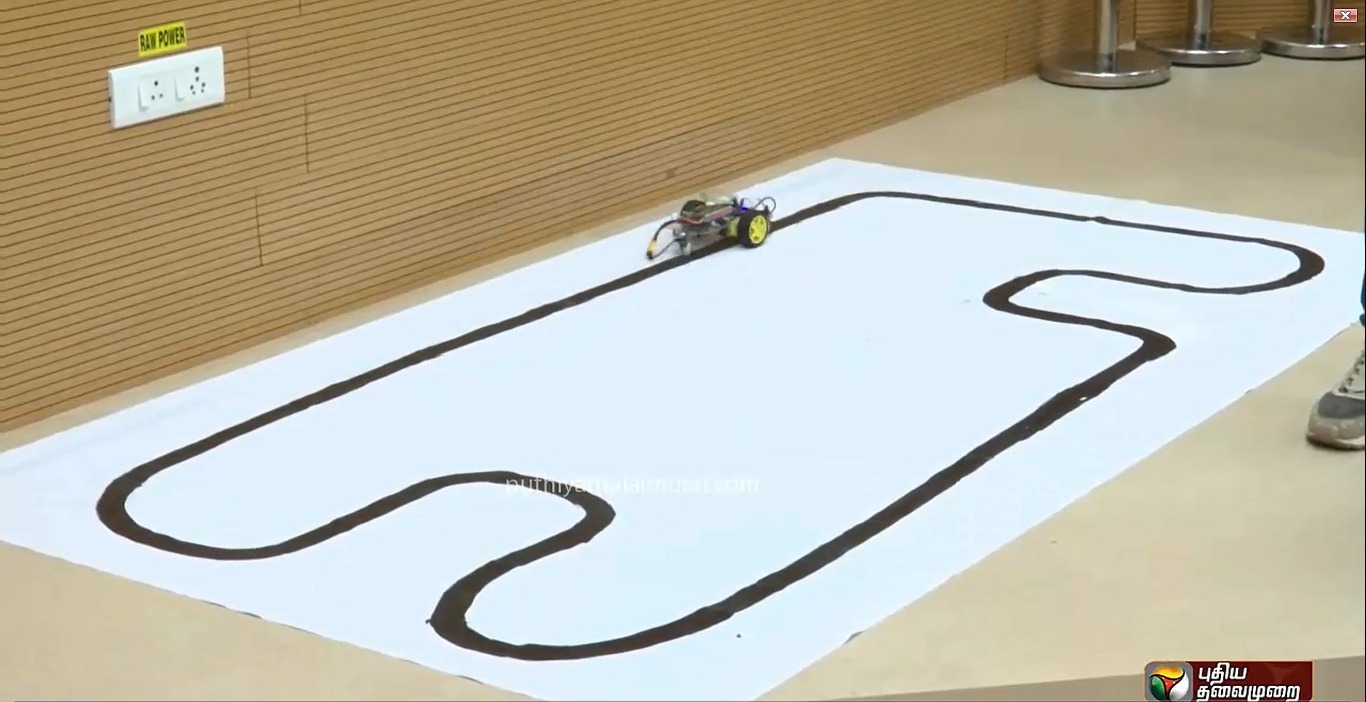

VSDSquadron Educational board on Tamil News channel

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Karnataka VLSI roadshow at Sahyadri College, Mangalore