Today, as technology races towards ever-smaller geometries and more complex chips, the need for professionals who are not just well-versed in theory but also skilled in practical, hands-on experience has never been more critical. An intense VLSI program that mirrors industry practices is the beacon that guides aspiring engineers across this bridge.

Sharing a sample repository of past student from SFAL-VSD program

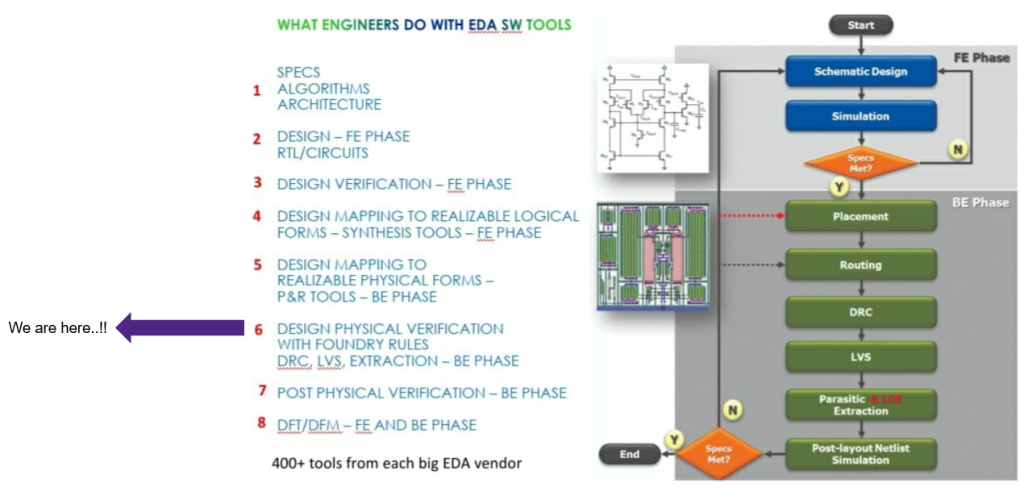

The Journey through EDA Tools in Chip Design

The above image encapsulates the structured journey an engineer traverses in the landscape of chip design using EDA tools. It underscores the sequential phases of chip design, beginning with the conceptualization of specs and algorithmic architecture. Progressing through the Front End (FE) phase, the focus shifts to the intricate tasks of design and verification, where engineers translate Register Transfer Level (RTL) descriptions into logical circuits. As the pathway advances, it reaches a crucial juncture—mapped in the image as the current location—where designs are transformed into physical forms through Placement & Routing (P&R) tools in the Back End (BE) phase. This meticulous progression is indicative of the comprehensive scope an engineer needs to master, from synthesis to post-physical verification, ensuring the design is fully prepared for the tapeout phase. This illustration vividly outlines the crucial benchmarks of chip design, delineating the vast array of over 400 tools available from prominent EDA vendors, thus highlighting the depth and complexity of the field.

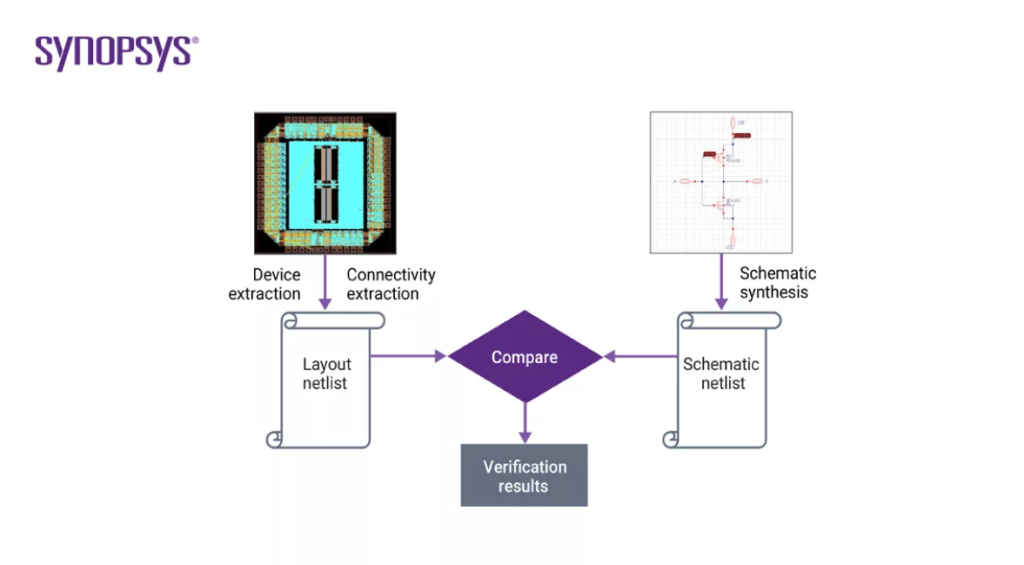

Synopsys’ Verification Process

In this image, Synopsys presents a refined focus on the verification phase of chip design, illustrating the essential steps of ensuring the layout’s fidelity to the original schematic. The process initiates with device and connectivity extraction from the physical layout, leading to the generation of a layout netlist. Concurrently, schematic synthesis yields a corresponding schematic netlist. These two netlists then undergo a rigorous comparison, ensuring that the schematic intentions are accurately translated into the physical layout. This step is pivotal in the design flow and is reflective of the meticulous attention to detail required in the verification process. It serves as a testament to the importance of precision in the design of integrated circuits, and the verification results serve as a quality checkpoint before proceeding to subsequent stages.

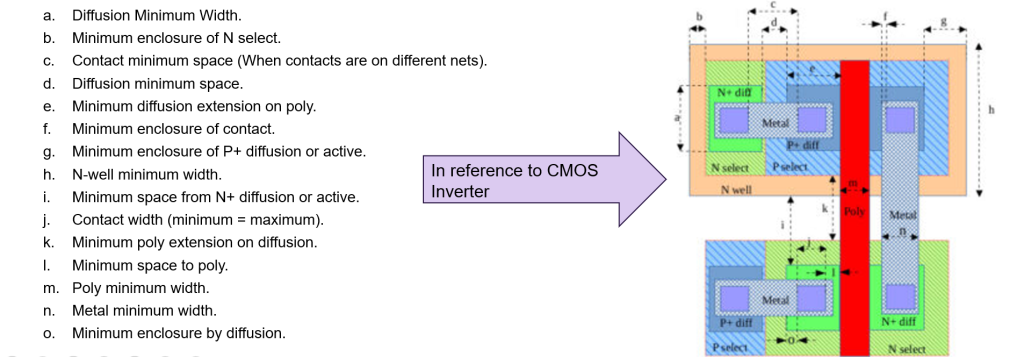

CMOS Inverter Design Rules

The third image is a deep dive into the world of design rules specific to a CMOS inverter—a fundamental building block in digital circuits. It lists the myriad of parameters, such as minimum widths and spacings, that are vital to the physical realization of semiconductor devices. Each rule corresponds to the geometrical and topological constraints of the CMOS inverter’s layout, ensuring that the device will not only be manufacturable but also perform reliably. This layout adheres to stringent design rules such as diffusion widths, spacing between contacts, and the enclosure requirements for various layers. The adherence to these rules is paramount in avoiding fabrication failures and ensuring the inverter’s functionality. This image provides an invaluable reference for engineers, distilling the essence of complex fabrication design rules into a comprehensive visual guide.

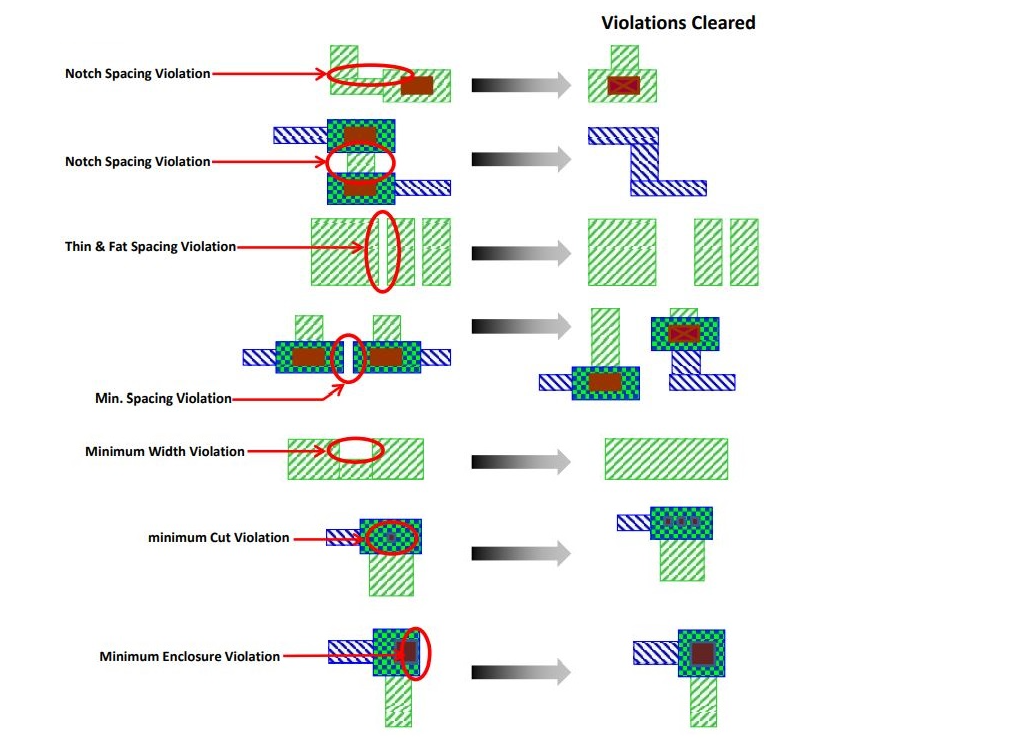

Correcting Design Rule Violations

This image vividly portrays the iterative process of identifying and correcting design rule violations, a critical aspect of ensuring a manufacturable chip. Displaying common DRC violations, such as notch spacing, thin and fat spacing, and minimum width constraints, it illustrates the corrective actions necessary to adhere to the stringent standards of integrated circuit design. This step-by-step resolution of errors demonstrates the practical challenges faced during the layout phase and the importance of DRC in the VLSI design process. The image reinforces the continuous loop of validation and refinement that is essential to achieving a defect-free design, indicative of the high-quality standards maintained in the semiconductor industry. It serves as a stark reminder of the complexity and precision required in the chip fabrication process, and the relentless pursuit of perfection that defines the field.

SFAL-VSD Program link

Related Posts:

- Smart Plant Care using the VSD_Squadron-MINI-BOARD

- Accelerating the Future of Semiconductor Talent with…

- Bluetooth automated smart access

- Home safety system

- RISC-V Mini Game Console

- The Future of Chip Design: The Next Generation is…

- Water level monitoring and control in water tank

- Shape Tomorrow’s Technology Today: ELCIA Hackathon…

- Secure Saiyan

- Advanced Easy to use Burgler Alarm