Find all repository at

10 bit ADC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

General purpose Bandgap

Clock multiplier (pll) (Fclkin – 5MHz to 12Mhz, Fclkout – 40MHz to 100MHz at 1.8v

Crystal oscillator analog pads (3.3V, Fclkout-1MHz-4MHz)

Lower power current programmable CMOS comparator with hysteresis

Bi-directional Buffer with Non-Inverting CMOS Input and Gated Pull-down and Pull-up, Strength 4mA @ 3.3V, Normal, High noise (Fast speed)

SRAM (1024 x 32): (32kbits or 4kB), 1.8V and access time is <2.5ns

Open-source Layout Generator

Open-source Power Calculator

An automated RTL2GDS open-source flow

VSD, standing as a trailblazing Semiconductor EdTech company and a community-based Technology Aggregator, is revolutionizing the landscape of VLSI Design. With the belief that “Creativity is just connecting things”, VSD has mastered the art of linking the right resources with the community. This unique approach has sparked a significant transformation in the VLSI Design process.

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Job Roles, Convergence With Embedded Systems, and Startups

VSD showcased at Semicon India 2023

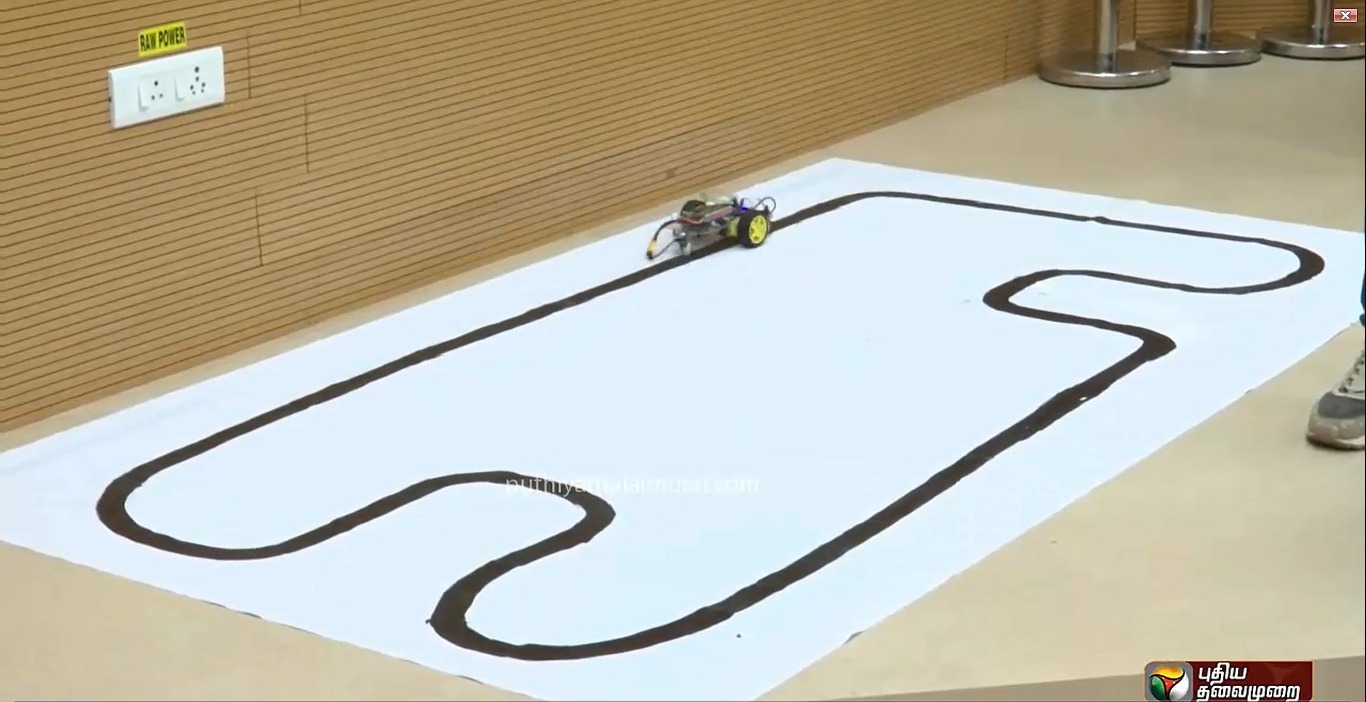

VSDSquadron Educational board on Tamil News channel

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Karnataka VLSI roadshow at Sahyadri College, Mangalore