Welcome to the World’s only online conference in Semiconductor Industry VSDOpen Conference 2019. With enormous support and global presence of audience from different segments of industrial lobby and academia made this a highly successful event.

Evolution is change in the genetic makeup of a population over time, online conference is one kind evaluation everyone adapt soon.

Please find the presentation by our Keynote Speakers and all selected papers :

Keynote 1 : Open-Source EDA for RTL-to-GDS Implementation: Updates and Futures – Prof. Andrew B. Kahng, UCSD Depts. of CSE and ECE

Andrew B. Kahng is Professor of CSE and ECE and holder of the endowed chair in high-performance computing at UC San Diego. He was visiting scientist at Cadence (1995-97) and founder/CTO at Blaze DFM (2004-06). He is coauthor of 3 books and over 500 journal and conference papers, holds 34 issued U.S. patents, and is a fellow of ACM and IEEE. He has served as general chair of DAC, ISPD and other conferences, and from 2000-2016 as international chair/co-chair of the ITRS Design and System Drivers working groups. He is currently PI of “OpenROAD” https://theopenroadproject.org/, a $12.4M U.S. DARPA project targeting open-source, autonomous (“no human in the loop”) tools for IC implementation.

Andrew B. Kahng is Professor of CSE and ECE and holder of the endowed chair in high-performance computing at UC San Diego. He was visiting scientist at Cadence (1995-97) and founder/CTO at Blaze DFM (2004-06). He is coauthor of 3 books and over 500 journal and conference papers, holds 34 issued U.S. patents, and is a fellow of ACM and IEEE. He has served as general chair of DAC, ISPD and other conferences, and from 2000-2016 as international chair/co-chair of the ITRS Design and System Drivers working groups. He is currently PI of “OpenROAD” https://theopenroadproject.org/, a $12.4M U.S. DARPA project targeting open-source, autonomous (“no human in the loop”) tools for IC implementation.

Keynote 2 : Growing Momentum and Opportunity of RISC-V Open Architecture, Calista Redmond, CEO RISC-V Foundation

Calista Redmond is the CEO of the RISC-V Foundation with a mission to expand and engage RISC-V stakeholders, compel industry adoption, and increase visibility and opportunity for RISC-V within and beyond the Foundation. Prior to the RISC-V Foundation, Calista held a variety of roles at IBM, including Vice President of IBM Z Ecosystem where she led strategic relationships across software vendors, system integrators, business partners, developer communities, and broader engagement across the industry. Calista’s background includes building and leading strategic business models within IBM’s Systems Group through open source initiatives including OpenPOWER, OpenDaylight, and Open Mainframe Project. Prior to IBM, she was an entrepreneur in four successful start-ups in the IT industry. Calista holds degrees from the University of Michigan and Northwestern University.

Calista Redmond is the CEO of the RISC-V Foundation with a mission to expand and engage RISC-V stakeholders, compel industry adoption, and increase visibility and opportunity for RISC-V within and beyond the Foundation. Prior to the RISC-V Foundation, Calista held a variety of roles at IBM, including Vice President of IBM Z Ecosystem where she led strategic relationships across software vendors, system integrators, business partners, developer communities, and broader engagement across the industry. Calista’s background includes building and leading strategic business models within IBM’s Systems Group through open source initiatives including OpenPOWER, OpenDaylight, and Open Mainframe Project. Prior to IBM, she was an entrepreneur in four successful start-ups in the IT industry. Calista holds degrees from the University of Michigan and Northwestern University.

Keynote 3: Fabless: The Transformation of the Semiconductor Industry, Daniel Nenni Founder of Semiwiki

Biodata: Daniel has worked in Silicon Valley for the past 35 years with semiconductor manufacturers, electronic design automation software, and semiconductor intellectual property companies.Daniel Nenni is the founder of SemiWiki.com (an open forum for semiconductor professionals) and the co-author and publisher of “Fabless: The Transformation of the Semiconductor Industry”, “Mobile Unleashed: The Origin and Evolution of ARM Processors in our Devices”, “Prototypical: The Emergence of Prototyping for SoC Design”, “Custom SoCs for Iot: The Emergence of Custom Silicon for IoT Devices” and “SoC Emulation Bursting into its Prime”.Daniel is an internationally recognised business development professional for companies involved with the fabless semiconductor ecosystem.

Invited Talks by Industry and Academia Expertise

First Talk by Industry Expertise : Zvonimir Z. Bandić,Chairman of CHIPS Alliance, Chair of OpenCAPI org, and Board of Directors member of RISC-V standards organisation

Biodata: Zvonimir Z. Bandić is the Research Staff Member and Senior Director of Next Generation Platform Technologies Department in a Western Digital Corporation in San Jose, California. He received his BS in electrical engineering in 1994 from the University of Belgrade, Yugoslavia, and his MS (1995) and PhD (1999) in applied physics from Caltech, Pasadena, in the field of novel electronic devices based on wide bandgap semiconductors.He is currently focusing on emerging Non-Volatile Memories (PCM, ReRAM, MRAM) applications for data center distributed computing, including RISC-V based CPU technologies, in-memory compute, RDMA networking, and machine learning hardware acceleration. He has been awarded over 50 patents in the fields of solid-state electronics, solid state disk controller technology, security architecture and storage systems and has published over 50 peer-reviewed papers.

Biodata: Zvonimir Z. Bandić is the Research Staff Member and Senior Director of Next Generation Platform Technologies Department in a Western Digital Corporation in San Jose, California. He received his BS in electrical engineering in 1994 from the University of Belgrade, Yugoslavia, and his MS (1995) and PhD (1999) in applied physics from Caltech, Pasadena, in the field of novel electronic devices based on wide bandgap semiconductors.He is currently focusing on emerging Non-Volatile Memories (PCM, ReRAM, MRAM) applications for data center distributed computing, including RISC-V based CPU technologies, in-memory compute, RDMA networking, and machine learning hardware acceleration. He has been awarded over 50 patents in the fields of solid-state electronics, solid state disk controller technology, security architecture and storage systems and has published over 50 peer-reviewed papers.

Second Talk by Academia Expertise : Dr. V. Kamakoti, Professor IIT Madras, Associate Dean ICSR,National Security Advisor Board Member

Dr. V. Kamakoti received the M.S. degree and the Ph.D. degree in computer science and engineering from IIT Madras, Chennai, India. He is currently a Professor with the Department of Computer Science and Engineering and Associate Dean at ICSR,IIT Madras. He has more than 15 years of experience in computer systems development and specializes in the area of computer architecture, CAD for VLSI, and high-performance computing.Dr. Kamakoti took India’s first RISC-V based SHAKTI Processor initiative which aim to break the barrier between Academia and Industry by providing open-source Processor and SoC designs. He has authored a number of research papers that have been published in various international journals and in the PROCEEDINGS of many scientific conferences. Dr. Kamakoti also has interest in writing literature and has published Ganiporiyum Adipadiyum, a book in Tamil released in 1992.Dr. Kamakoti was research guide for 10 PhD students who have already graduated and 9 are ongoing. The paper entitled A Parallel Genetic Approach, using artificial neural networks, to temporal partitioning and synthesis for reconfigurable architectures won the Excellent Presentation Award at the Third Inter- national Symposium on Advanced Intelligent Systems (ISIS) held at Tsukuba, Japan, 2002.Dr. Kamakoti received DRDO Academic Excellence Award instituted by DRDO in recognition of the contribution from Academicians to various programs of DRDO. Recently, Dr. Kamakoti was awarded Techno Visionary Award, which is a lifetime achievement award given to an Indian academician, who made significant contributions to the field of Electronics and Semiconductor through research and development.

LIVE Open Source HW Demo Booth

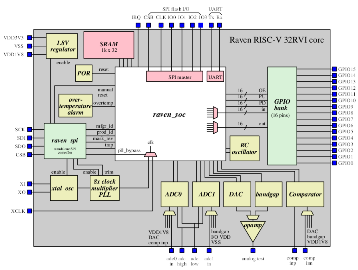

Demo 1 : Raven Chip – First-time silicon success with Qflow and Efabless : JEFF DICORPO, SVP Business Development and Strategic Partnerships at Efabless

- Raven is a open-source top-level SoC design based on an open-source RISC-V core

- Complete SoC design including digital and analog IP

- Build using a open-source design flow successfully implemented in silicon using X-FAB’s 180nm XH018 process

- The project is available through github including testbenches and development board

- Users can also clone the project on the Efabless platform to create derivative designs

- The raven chip contains two ADCs, a DAC, comparator, bandgap, RC oscillator, and over-temperature alarm, as well as 16 bits of general-purpose digital inputs/outputs.

- It is powered off of a single 3.3V supply and driven by a 5 to 12 MHz crystal. The core CPU clock speed is 8 times the crystal frequency.

Demo 2 : The PULP project in 15 minutes, Serious open source hardware for everyone by Frank K. Gürkaynak, ETH Zürich

What is Parallel Ultra Low Power (PULP)?

- Research project on Energy Efficient Computer Architectures

- Started in 2013, by Luca Benini

- ETH Zürich, Switzerland and University of Bologna, Italy

- Results available as open source hardware

- At Github: https://github.com/pulp-platform

- Under permissive (Apache like) Solderpad license

- At the moment, there we have 36 ASICstaped out

- 6x 22nm, 4x 28nm, 1x 40nm, 15x 65nm, 5x 130nm, 5x180nm

Demo 3: BOOM: The Berkeley Out-of-Order Machine by Berkeley University

- Superscalar RISC-V OoO core

- Fully integrated in Rocket Chip ecosystem

- ~18K LoC of open-source Chisel

- Parameterizable generator

- Taped-out (BROOM at HC18)

- Full RV64GC ISA support

- FP, RVC, Atomics, PMPs, VM, Breakpoints, RoCC

- Runs real OS’s (Fedora, BR Linux), software

- Drop-in replacement for the Rocket core

- Licensed under Apache 2.0

Invited Talks by Open Source Tool Developers

Talk by Steve Hoover on “Unleashing Open Source Silicon”

Steve Hoover is the founder of Redwood EDA. Steve holds a BS in electrical engineering from Rensselaer Polytechnic Institute and an MS in computer science from the University of Illinois. He has designed numerous components for high-performance server CPUs and network architectures for DEC, Compaq, and Intel. With Redwood EDA, Steve is introducing advanced digital design methodology and provides the open-source silicon community with the makerchip.com development platform.

Steve Hoover is the founder of Redwood EDA. Steve holds a BS in electrical engineering from Rensselaer Polytechnic Institute and an MS in computer science from the University of Illinois. He has designed numerous components for high-performance server CPUs and network architectures for DEC, Compaq, and Intel. With Redwood EDA, Steve is introducing advanced digital design methodology and provides the open-source silicon community with the makerchip.com development platform.

Talk by Puneet Goel on ” Embedded UVM – Enabling Multicore Test benches”

Puneet Goel is a 1994 graduate in Electronics from Punjab Engineering College. He has 24 years of experience in the VLSI industry where he worked for STMicro, Motorola, Texas Instruments and TranSwitch. For the past 8 years, he has been working for Coverify Systems Technology, where he provides verification services and works on creating viable opensource solutions for chip verification. Puneet is the main developer of Embedded UVM – Enabling Multicore Testbenches .

Puneet Goel is a 1994 graduate in Electronics from Punjab Engineering College. He has 24 years of experience in the VLSI industry where he worked for STMicro, Motorola, Texas Instruments and TranSwitch. For the past 8 years, he has been working for Coverify Systems Technology, where he provides verification services and works on creating viable opensource solutions for chip verification. Puneet is the main developer of Embedded UVM – Enabling Multicore Testbenches .